# Fundamental Digital Module Realization Using RTL Design for Quantum Mechanics

Chandrakumar Rasanjani<sup>1</sup>, Anuradha K. Madugalla<sup>2</sup>, Manthila Perera<sup>3</sup>

<sup>1-3</sup>Department of Electrical Engineering Faculty of Engineering, University of Moratuwa Moratuwa, Sri Lanka

#### **KEYWORDS:**

Binary Square rooter; Conventional logic; Energy Efficient; Low power; Non-restoring algorithm; Reversible.

#### ARTICLE HISTORY:

Received 14.07.2022 Accepted 11.08.2022 Published 24.09.2022

DOI: https://doi.org/10.31838/jvcs/05.02.01

#### **Abstract**

Calculation of square root will be an essential mathematical operation that will have broad applications. In Hardware, the square root will be designed in order to gain power which will be quite low. Similarly, there are also other advantages that comes with gaining of low power that is high speed and also low area. A trade-off will also occur with the three metrics which is guite natural. As we know that the present technology is very advanced so it will aim for low power and architectural modification will be required by the relative designs. This sheet represents an energy efficient square rooter by using reversible logic. (RCSM) Reversible Controlled Subtract Multiplexer will be designing and it also plays an important part in implementing the binary square rooter. Saimur Rahman Gate will also be implementing the binary square rooter in order to improve and develop it. The Improvements such as cost of the quanta, inputs given by constants and also garbage outputs. The approaches such as conventional approach and SRG are used for designing the binary square rooter and it will be completed using non-restoring algorithm. Xilinx Software will be responsible for carrying out simulations and Synopsys Design Compiler will be the factor for obtaining power. The gate count which has been 75 will be decreased to 35. There will be an improvement of 20% in terms of power which will be obtained in this paper.

Author's e-mail: chandr.rasanjani@elect.mrt.ac.lk, k.anuradha@elect.mrt.ac.lk, perera.manthila@elect.mrt.ac.lk

**How to cite this article:** Rasanjani C, Madugalla AK, Perera M. Fundamental Digital Module Realization Using RTL Design for Quantum Mechanics. Journal of Complementary Research, Vol. 5, No. 2, 2023 (pp. 1-7).

# INTRODUCTION

Square root is considered to be one of the essential mathematical operation. They are involved in a wide range of applications namely data processing, computer graphics, DSP(digital signal processing) a global positioning system (GPS), and many mathematical calculations. For portable and wireless devices, Low power is the basic necessity. Square rooters in use for many years for various purposes. We use reversible logic in our design to attain low power. The number of input ports and output port is not uniform in Irreversible logics, and therefore it resulted in the loss of information bits. A single bit present in the information dissipates kTln2 Joules of energy which was proposed by Launders Theorem.<sup>[1]</sup> To avoid the loss of information bits and energy loss, reversible logic is used.<sup>[2]</sup> The loss of heat can be avoided by keeping the number of input and output ports present in the reversible logic in a uniform

Journal of VLSI circuits and systems, , ISSN 2582-1458

manner. Power consumption will be reduced in square rooter. A reversible nonlinear feedback shift register will be developed by a low power Authors in.<sup>[3]</sup>

The calculation of square root can be performed either by restoring or non-restoring using the digitby-digit technique. The methods proposed by Newton Rapshon and Goldschmidt<sup>[4]</sup> requires more hardware resources and has many steps involved than the digits by digits method. More hardware resources are necessary for restoring the approach. Hardware will be consumed less in the non-restoring process,<sup>[5]</sup> when compared to restoring practice. So thereby, Square root will select non-restoring process. Many hardware architectures which use irreversible logic has been proposed for digitby-digit technique. Array-based arithmetic<sup>[6]</sup> computation can also be able to reduce power. In calculating square root in,<sup>[7]</sup> the design of hardware realization of nonrestoring algorithm will be done by reversible logic. The power obtained was high. Computation of Square root requires many reversible logic circuits.

In restoring method, the circuit adds the divisor back and put "0" as the circuit's next quotient digit. Whereas in the non-restoring process, there is no mechanism like that. So, the negative remainder and the number "01" are added and radically right things by a supplementary addition later.

A significant part of the existing algorithms, such as BDD based realization, Positive Polarity Reed Mullerare, is restricted to small and medium process though optimized in gate counts and information bits. In contrast, some realization methods succeed in addressing large functions but expensive in terms of additional gate lines, gate counts and quantum price, mainly from the specifications of irreversible logic. Moreover, exceptional work has done towards realizing the essential reversible computation units like adders, subtractors and multipliers by obtaining a straight translation from traditional to reversible forms. Square-root is most valuable and vital in scientific calculations next to fundamental mathematical operations, i.e. addition, subtraction, multiplication and division. For instance, statistical analysis, complex number calculations, logical analysis, machine graphics and visuals, and signal processing are among the fields where the square root operation is related. Although the understanding of a square root in traditional circuits is well organized. 8- bit binary square root network is a model of square root operation, not a stable structure or generalized approach of creating a reversible square root network. This paper proposes a structured approach for performing the computation circuit. The generation of the reversible embedding, which is an array arrangement of primary blocks, and can apprehend square root networks of any length. To be precise, the standard non-restoring array arrangement of square-root circuit, which operates 2's Complement subtraction regulated by the result of digitby-digit square root. The proposed design has a reversible controlled subtractor multiplexer(RCSM) block, which produces 2's Complement calculation, and applied in a modular technique to perform the operation of square root.

In Newton-Raphson's method or Heron's method, the solution of square root of a given number is calculated using the formula:

$$x(k+1)=(1/2)(xk+(a/xk))$$

(1)

where "a" is a number, whose square root value will be calculated and xk is iterative

## **PROPOSED MODELS**

Digit by digit procedure is used for obtaining a particular binary number's derived square root. Restoring algorithm and non-restoring algorithm are classified from digit G-by-digit procedure. The system's total power is high using the restoring algorithm because it involves a more significant number of hardware resources. When compared to restoring algorithm, the non-restoring algorithm involves a smaller number of hardware resources. The total number of bits N is divided into a group of two digits in the nonrestoring algorithm. Therefore, the length of the Quotient is N/2. Steps involving in the non-restoring algorithm are as follows:

- Step 1: Separation of the total bits of N into two parts.

- Step 2: From the leftmost group of significant bits we have to subtract '1'. If the subtraction will be positive, then Quotient will be 1, then if the difference will be negative, then the Quotient is 0.

- Step 3: From the next group of two digits, subtract after appending the previous quotient along with "01".

- Step 4: Until we reach till the last of groups of two digits we have to proceed to step -2.

It can be a whole number or radical number in case of radicand. Let us assume that it will be a decimal number, then it will be denoted like 0010.001...And if the radicand is going to be a whole number, then it will be denoted as 1101. In this, 0010 will be linked to 6 and 0011 will be pointed to 0.4 in terms of binary sign. On the basis of requirement the number of bits which are obtained after the decimal point will be prolonged to N that is the total number of bits.

Lets consider a binary square rooter (N7 N6 N5 N4. N3 N2 N1 N0). In Quotient for square rooter it will be going to be (U3 U2. U1 U0). The user can decide the number of bits previously and succeeding the decimal point. For example, the square root of 1101 and 0010.0011 is given in Fig.1.

From Fig. 1, the square root of 13 and 2.2 are found. Value for the square root obtained form 13 will be 3.6. From the quotient 11.10(U3 U2. U1 U0),11(U3U2) corresponds to 3 and 10 (U1U0) to 0.6. The representation of 0.6 in the binary system is 1001.Value obtained for the square root of 2.2(0010.0011) will be 1.4. And the value of the Quotient 01.01, 01(U3U2) will be represented to 1 and 01 (U1U0) to 0.4. The representation of 0.4 in the binary system is

Fig. 1: Non-Restoring Algorithm

0110. As mentioned, application and user requirement will be deciding count of bits previously and after the decimal point. If there will be a large number of requirement in significant number of bits in the Quotient, then the user shall increases bit size after the decimal point to fulfil the requirement.

A reversible full subtractor is required for computation process which will be done by non-restoring algorithm. The gates like Feynman Gate and Saimur Rahman gate will be designing the square rooter. a full subtractor will be the serviceability of the Saimur Rahman gate. It is clearly presented in the Fig. 1.

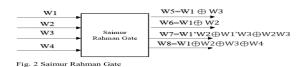

### Saimur Rahman Gate

A Three bit (3-bit) subtractor is called a Full subtractor. It has 3 inputs, W1, W2, W3 and another input, W4=0 and two outputs difference as W8 and borrows as W7. The mathematical expressions for difference and borrow are

- Difference (W8) =W1-W2-W3

- Borrow W7=1 if W1<(W2-W3) else W7=0</li>

The logical expressions for difference and borrow are

- Difference (W8) = W1 W2 W3 W4

- Borrow W7=W1'W2□W1'W3⊕W2W3

where  $\oplus$  is Logical XOR operation and W1 'represents compliment operation of W1.

Only in the case of W4=0, a full subtractor will be used which comes from the SRG gate, and also in case of W4 is not equal to 0, in that case, the gate will not be able to work as full subtractor. Garbage output will be represented by W5 and W6. Table.1 will be representing the truth table of SR gate. The radicands ( $N_7 N_6 N_5 N_4 N_3 N_2 N_1 N_0$ ). with a total length of 8 binary bits. the number of binary bits for the Quotient is half of 8 in the essence of 8/2= 4( $U_3 U_2$ .  $U_1 U_0$ ) 8-bit square rooter. FG and SR gates will be implemented with the 8-bit square rooter.

### **Reversible Multiplexer**

A multiplexer allows many incoming signals to interact with one device, circuit or resource. Multiplexers also used for the implementation of multiple variable's Boolean functions. The realization of a Multiplexer using reversible logic gates is called a Reversible multiplexer. The proposed design has RT reversible logic gate multiplexer.

If the remainder will be taken as positive, and then the Quotient, i.e. U=1 and the difference will be carried over for the following according to non-restoring computation. But in case if the remainder is taken as negative, then the Quotient will be (U=0), and the previous inputs will then be carried for the following procedure, By using RT reversible gate, a control unit is designed to interchange between the inputs(W1) and the difference(W1). The input(W1), the difference (W8) and the Quotient will given as input to the

Fig. 2: SRG Gate

Table 1: Samiur Rahman Gate (SRG) Truth Table

| $\mathbf{W}_1$ | $\mathbf{W}_2$ | $W_3$ | $W_4$ | $\mathbf{W}_7$ | $\mathbf{W}_8$ |

|----------------|----------------|-------|-------|----------------|----------------|

| 0              | 0              | 0     | 0     | 0              | 0              |

| 0              | 0              | 1     | 0     | 1              | 1              |

| 0              | 1              | 0     | 0     | 1              | 1              |

| 0              | 1              | 1     | 0     | 1              | 0              |

| 1              | 0              | 0     | 0     | 0              | 1              |

| 1              | 0              | 1     | 0     | 0              | 0              |

| 1              | 1              | 0     | 0     | 0              | 0              |

| 1              | 1              | 1     | 0     | 1              | 1              |

gates. For the process of switching among the inputs and the difference we use reversible multiplex.

Based on the Quotient we can be able to see the configuration which is shown in Fig. 3. The difference and the input will be auto switched. Non-restoring algorithm will be proposed by the design with the help of these reversible gates. The basic logic gates OR,XOR,NOT,AND being applied to the traditional approach. We use irreversible gates for the administration of the conventional design. We can finally obtain the power outcomes of conventional and reversible designs.

#### WORKING OF SQUARE ROOT

Figure 3 depicts that the square root of a binary number can be observed with the help of the Modified Nonrestoring algorithm by using the digit-by-digit approach. By using the modified non-restoring algorithm, the provided binary digit is primarily separated into collections of two numbers. Soon "1" is deducted from the left-most significant digits (N7 N6), being the initial step. Next, if the deducted number is zero or greater than zero, the quotient(U3) is regarded as "1", and the RT reversible multiplexer transfers the variation value received of the gate essentially "d" bits (D1D2...) to the next step. Where (D1D2...) are difference bits

If the subtracted value is less than zero, i.e. negative, the quotient(U3) is regarded as "0". The reversible multiplexer transfers the former input data bit to the following step; along with the value received of the previous level, the next couple of bits are considered simultaneously with that value. Those values were saved as "A" bits (A1A2A3...).

The quotient from the preceding step and "01" is added and stocked as B bits (B1B2...), and B bits are deducted from A bits, and this process is iterated till all the digits are finished. The Square root of the provided binary number

Fig. 3: 8-bit Binary Square Root

Fig. 4: RT Multiplexer

is the terminal quotient, which is the input provided by the user to the circuit. The additional outputs are garbage outputs(G1G2...).

Therefore, using reversible gates such as RT reversible multiplexer, Samiur Rahman Gate (SRG) works as a multiplexer and full subtractor, respectively, by following the Non-restoring algorithm, the square root of a binary number is obtained.

# EXPERIMENTAL FINDINGS AND RESULTS OF SIMULATION

#### Comparison with other methods

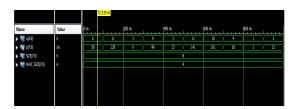

VHDL language has been used for coding of the proposed design. Verification of outputs received from respective inputs are processed. If the input radicand is 36, the Quotient is 6, it is observed that from the simulation results shown in Fig4.1. As soon as the design which is proposed will be compiled, the power result is obtained using 90nm technology that is Synopsys Design Compiler for reversible design. From Fig.4.1, Fig. 7 and Table. II we can observe the power and area derived.

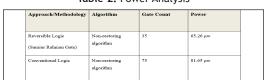

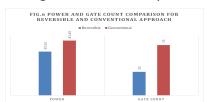

Table 2 shows the comparison between the Conventional model and SRG reversible logic model. After Comparing the two models independently, Reversible Logic (SRG) demands fewer logic gates than the Conventional reversible logic based on the non-restoring algorithm for developing the solution for square root.

#### Fig. 5: Simulation output

# Fig. 6: Reversible logic and Conventional logic comparison

Table 3: Design summary

| Device Utilization Summary (estimated values) |      |           |             |  |  |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |  |  |

| Number of Slice LUTs                          | 6    | 204000    | 0%          |  |  |  |  |

| Number of fully used LUT-FF pairs             | 0    | 6         | 0%          |  |  |  |  |

| Number of bonded IOBs                         | 12   | 600       | 2%          |  |  |  |  |

Fig. 7: Time summary

Fig. 8: Binary Square root unit

Xilinx Software will be responsible for carrying out simulations and Synopsys Design Compiler will be the factor for obtaining power. The gate count which has been 75 will be decreased to 35. There will be an improvement of 20% in terms of power.

The Reversible logic RSG model utilizes 65.26 microwatts of power to complete the operation of the square root by measuring the power consumption by the proposed RSG reversible logic model. In contrast, the existing model utilized 81.65 microwatts of power, a

Table 2: Power Analysis

4

20.0735 change in percentage. Hence, by implementing the energy-efficient binary square root by a non-restoring reversible logic, 20 per cent of power(energy or electricity) is conserved.

The above Design summary table gives information regarding the device utilization on basis of their utilization percentage and their availability of LUT's, LUT-FF pairs and bonded IOB'S.

Time summary of the project shows the timing constraints, total number of paths are 26, destination ports are 4 with 1.175 ns delay. In the time summary delays of each unit and entire model with their gate delays and net delays are represented.

# Applications

Various fields have applications based on Reversible logic design, including optical computing, Quantum computing, Quantum Computing Automata, Nanocomputing. The research of measurable targets termed as Abstract tools and the computational obstacles that can be resolved using Quantum Computing is Quantum Computing Automata. Other applications of reversible logic design are ultra-low-energy-efficient Very Large Scale Integration(VLSI) designing, Quantum Dot Cellular Automation. An alternative for the limitations of Moore's law on the expectation of computer chip designing; is to formulate quantum chips with the help of reversible logic design. Our ultimate research problem is planning a modern reversible gate, including the implementation towards the perfect Quantum processor that is competent in working with barely energy-efficient computing. It also looks forward in working with high-speeds.

Implementation of an energy-efficient binary square rooter using Reversible logic by applying the non-restoring algorithm can be used for Statistical Analysis purposes, Complex Number Calculations, Logical Analysis of digital machines, Machine Graphics, Signal Processing through the digital binary method.

# CONCLUSION

Binary square root using SRG reversible logic implementation was designed, and the Proposed model and existing model properties are compared. Binary Square root implementation based on a non-restoring algorithm provides the solution with less number of gates and energy efficiency. Resolutions of the proposed model are very adaptable. Minor changes in VHDL code can accomplish the demands of extending the number of bits and number of decimal places after the floating point. The approaches such as conventional approach and SRG are used for designing the binary square rooter and it will be completed **Prig. 9: Reversibles algorithm** Silvare of bits and Synopsys Design Compiler will be the factor for obtaining power. The gate count which has been 75 will be decreased to 35. There will be an improvement of 20% in terms of power which will be obtained in this paper. Hardware will be consumed less in the non-restoring process, when compared to restoring practice. So thereby, Square root will select non-restoring process. Thus, with all the necessary parameters an energy efficient reversible binary square rooter was successfully implemented. ALUs will be using square rooter for reversible computing especially for reversible computing. There will be a decrease in the gate count and also the conventional approach will be consuming more power when compared with reversible computing.

# REFERENCES

- [1] Dr. S. Selvakanmani, Mr. Rajeev Ratna Vallabhuni, Ms. B. Usha Rani, Ms. A. Praneetha, Dr. Urlam Devee Prasan, Dr. Gali Nageswara Rao, Ms. Keerthika. K, Dr. Tarun Kumar, Dr. R. Senthil Kumaran, Mr. Prabakaran.D, "A Novel Global Secure Management System with Smart Card for IoT and Cloud Computing," The Patent Office Journal No. 06/2021, India. International classification: H04L29/08. Application No. 202141000635 A.

- [2] Nalajala Lakshman Pratap, Rajeev Ratna Vallabhuni, K. Ramesh Babu, K. Sravani, Bhagyanagar Krishna Kumar, Angothu Srikanth, Pijush Dutta, Swarajya Lakshmi V Papineni, Nupur Biswas, K.V.S.N.Sai Krishna Mohan, "A Novel Method of Effective Sentiment Analysis System by Improved Relevance Vector Machine," Australian Patent AU 2020104414. 31 Dec. 2020

- [3] S.V.S Prasad, Chandra Shaker Pittala, V. Vijay, and Rajeev Ratna Vallabhuni, "Complex Filter Design for Bluetooth Receiver Application," In 2021 6th International Conference on Communication and Electronics Systems (ICCES), Coimbatore, India, July 8-10, 2021, pp. 442-446.

- [4] Chandra Shaker Pittala, J. Sravana, G. Ajitha, P. Saritha, Mohammad Khadir, V. Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Novel Methodology to Validate DUTs Using Single Access Structure," 5th International Conference on Electronics, Materials Engineering and Nano-Technology (IEMENTech 2021), Kolkata, India, September 24-25, 2021, pp. 1-5.

- [5] Chandra Shaker Pittala, M. Lavanya, V. Vijay, Y.V.J.C. Reddy, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Energy Efficient Decoder Circuit Using Source Biasing Technique in CNTFET Technology," 2021 Devices for Integrated Circuit (DevIC), Kalyani, India, May 19-20, 2021, pp. 610-615.

- [6] Chandra Shaker Pittala, M. Lavanya, M. Saritha, V. Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Biasing Techniques: Validation of 3 to 8 Decoder Modules Using 18nm FinFET Nodes," 2021 2nd International Conference for Emerging Technology (INCET), Belagavi, India, May 21-23, 2021, pp. 1-4.

- [7] P. Ashok Babu, V. Siva Nagaraju, Ramya Mariserla, and Rajeev Ratna Vallabhuni, "Realization of 8 x 4 Barrel shifter with 4-bit binary to Gray converter using FinFET for Low

Power Digital Applications," Journal of Physics: Conference Series, vol. 1714, no. 1, p. 012028. IOP Publishing. doi:10.1088/1742-6596/1714/1/012028

- [8] Vallabhuni Vijay, C. V. Sai Kumar Reddy, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, M. Saritha, M. Lavanya, S. China Venkateswarlu and M. Sreevani, "ECG Performance Validation Using Operational Transconductance Amplifier with Bias Current," International Journal of System Assurance Engineering and Management, vol. 12, iss. 6, 2021, pp. 1173-1179.

- [9] Vallabhuni, Rajeev Ratna, M. Saritha, Sruthi Chikkapally, Vallabhuni Vijay, Chandra Shaker Pittala, and Sadulla Shaik, "Universal Shift Register Designed at Low Supply Voltages in 15 nm CNTFET Using Multiplexer," In International Conference on Emerging Applications of Information Technology, pp. 597-605. Springer, Singapore, 2021.

- [10] B. M. S. Rani, Vallabhuni Rajeev Ratna, V. Prasanna Srinivasan, S. Thenmalar, and R. Kanimozhi, "Disease prediction based retinal segmentation using bi-directional ConvLSTMU-Net," Journal of Ambient Intelligence and Humanized Computing, 2021, pp. 1-10. https://doi. org/10.1007/s12652-021-03017-y

- [11] Rajeev Ratna Vallabhuni, A. Karthik, CH. V. Sai Kumar, B. Varun, P. Veerendra, and Srisailam Nayak, "Comparative Analysis of 8-Bit Manchester Carry Chain Adder Using FinFET at 18nm Technology," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), Thoothukudi, India, 2020, pp. 1579-1583, doi: 10.1109/ ICISS49785.2020.9316061.

- [12] R. R. Vallabhuni, P. Shruthi, G. Kavya and S. Siri Chandana, "6Transistor SRAM Cell designed using 18nm FinFET Technology," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), Thoothukudi, India, 2020, pp. 1584-1589, doi: 10.1109/ICISS49785.2020.9315929.

- [13] Rajeev Ratna Vallabhuni, J. Sravana, M. Saikumar, M. Sai Sriharsha, and D. Roja Rani, "An advanced computing architecture for binary to thermometer decoder using 18nm FinFET," 2020 Third International Conference on Smart Systems and Inventive Technology (ICSSIT), Tirunelveli, India, 20-22 August, 2020, pp. 510-515.

- [14] Rajeev Ratna Vallabhuni, K.C. Koteswaramma, B. Sadgurbabu, and Gowthamireddy A, "Comparative Validation of SRAM Cells Designed using 18nm FinFET for Memory Storing Applications," Proceedings of the 2nd International Conference on IoT, Social, Mobile, Analytics & Cloud in Computational Vision & Bio-Engineering (ISMAC-CVB 2020), 2020, pp. 1-10.

- [15] V. Siva Nagaraju, Rapaka Anusha, and Rajeev Ratna Vallabhuni, "A Hybrid PAPR Reduction Technique in OFDM Systems," 2020 IEEE International Women in Engineering (WIE) Conference on Electrical and Computer Engineering (WIECON-ECE), Bhubaneswar, India, 26-27 Dec. 2020, pp. 364-367.

- [16] V. Siva Nagaraju, P. Ashok babu, B. Sadgurbabu, and Rajeev Ratna Vallabhuni, "Design and Implementation of Low power FinFET based Compressor," 2021 3rd International Conference on Signal Processing and Communication (ICP-SC), Coimbatore, India, 13-14 May 2021, pp. 532-536.

- [17] P. Ashok Babu, V. Siva Nagaraju, and Rajeev Ratna Vallabhuni, "Speech Emotion Recognition System With Libro-

sa," 2021 10th IEEE International Conference on Communication Systems and Network Technologies (CSNT), Bhopal, India, 18-19 June 2021, pp. 421-424.

- [18] P. Ashok Babu, V. Siva Nagaraju, and Rajeev Ratna Vallabhuni, "8-Bit Carry Look Ahead Adder Using MGDI Technique," IoT and Analytics for Sensor Networks, Springer, Singapore, 2022, pp. 243-253.

- [19] Rajeev Ratna Vallabhuni, Jujavarapu Sravana, Chandra Shaker Pittala, Mikkili Divya, B.M.S.Rani, and Vallabhuni Vijcaay, "Universal Shift Register Designed at Low Supply Voltages in 20nm FinFET Using Multiplexer," In Intelligent Sustainable Systems, pp. 203-212. Springer, Singapore, 2022.

- [20] V. Vijay, J. Prathiba, S. Niranjan Reddy, V. Raghavendra Rao, "Energy efficient CMOS Full-Adder Designed with TSMC 0.18µm Technology," International Conference on Technology and Management (ICTM-2011), Hyderabad, India, June 8-10, 2011, pp. 356-361.

- [21] Vallabhuni Vijay, Pittala Chandra shekar, Shaik Sadulla, Putta Manoja, Rallabhandy Abhinaya, Merugu rachana, and Nakka nikhil, "Design and performance evaluation of energy efficient 8-bit ALU at ultra low supply voltages using FinFET with 20nm Technology," VLSI Architecture for Signal, Speech, and Image Processing, edited by Durgesh Nandan, Basant Kumar Mohanty, Sanjeev Kumar, Rajeev Kumar Arya, CRC press, 2021.

- [22] P. Chandra Shaker, V. Parameswaran, M. Srikanth, V. Vijay, V. Siva Nagaraju, S.C. Venkateswarlu, Sadulla Shaik, and Vallabhuni Rajeev Ratna, "Realization and Comparative analysis of Thermometer code based 4-Bit Encoder using 18nm FinFET Technology for Analog to Digital Converters," In: Reddy V.S., Prasad V.K., Wang J., Reddy K.T.V. (eds) Soft Computing and Signal Processing. Advances in Intelligent Systems and Computing, vol 1325. Springer, Singapore. https://doi.org/10.1007/978-981-33-6912-2\_50

- [23] Rajeev Ratna Vallabhuni, S. Lakshmanachari, G. Avanthi, and Vallabhuni Vijay, "Smart Cart Shopping System with an RFID Interface for Human Assistance," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), Thoothukudi, India, 2020, pp. 165-169, doi: 10.1109/ICISS49785.2020.9316102.

- [24] Saritha, M., Kancharapu Chaitanya, Vallabhuni Vijay, Adam Aishwarya, Hasmitha Yadav, and G. Durga Prasad, "Adaptive And Recursive Vedic Karatsuba Multiplier Using Non Linear Carry Select Adder," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 22-29.

- [25] Vijay, Vallabhuni, Kancharapu Chaitanya, Chandra Shaker Pittala, S. Susri Susmitha, J. Tanusha, S. China Venkateshwarlu, and Rajeev Ratna Vallabhuni, "Physically Unclonable Functions Using Two-Level Finite State Machine," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 33-41.

- [26] Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, Vallabhuni Vijay, Usha Rani Anam, Kancharapu Chaitanya, "Numerical analysis of various plasmonic MIM/MDM slot waveguide structures," International Journal of System Assurance Engineering and Management, 2022.

- [27] M. Saritha, M. Lavanya, G. Ajitha, Mulinti Narendra Reddy, P. Annapurna, M. Sreevani, S. Swathi, S. Sushma, Vallabhuni Vijay, "A VLSI design of clock gated technique based ADC lock-in amplifier," International Journal of System

6

Assurance Engineering and Management, 2022, pp. 1-8. https://doi.org/10.1007/s13198-022-01747-6

- [28] Chandra Shaker Pittala, Vallabhuni Vijay, B. Naresh Kumar Reddy, "1-Bit FinFET Carry Cells for Low Voltage High-Speed Digital Signal Processing Applications," Silicon, 2022. https://doi.org/10.1007/s12633-022-02016-8.

- [29] Vallabhuni Vijay, Kancharapu Chaitanya, T. Sai Jaideep, D. Radha Krishna Koushik, B. Sai Venumadhav, Rajeev Ratna Vallabhuni, "Design of Optimum Multiplexer In Quantum-Dot Cellular Automata," International Conference on Innovative Computing, Intelligent Communication and Smart Electrical systems (ICSES -2021), Chennai, India, September 24-25, 2021.

- [30] S. China Venkateswarlu, N. Uday Kumar, D. Veeraswamy, and Vallabhuni Vijay, "Speech Intelligibility Quality in Telugu Speech Patterns Using a Wavelet-Based Hybrid Threshold Transform Method," International Conference on Intelligent Systems & Sustainable Computing (ICISSC 2021), Hyderabad, India, September 24-25, 2021.

- [31] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Low power based optimal design for FPGA implemented VMFU with equipped SPST technique," National Conference on Emerging Trends in Engineering Application (NCE-TEA-2011), India, June 18, 2011, pp. 224-227.

- [32] S. China Venkateswarlu, Ch. Sashi Kiran, R.V. Santhosh Nayan, Vijay Vallabhuni, P. Ashok Babu, V. Siva Nagaraju, "Artificial Intelligence Based Smart Home Automation System Using Internet of Things," The Patent Office Journal No. 09/2021, India. Application No. 202041057023 A.

- [33] Rajeev Ratna Vallabhuni, G. Yamini, T. Vinitha, and S. Sanath Reddy, "Performance analysis: D-Latch modules designed using 18nm FinFET Technology," 2020 International Conference on Smart Electronics and Communication (ICOSEC), Tholurpatti, India, 10-12, September 2020, pp. 1171-1176.

- [34] Rani, B.M.S, Divyasree Mikkili, Rajeev Ratna Vallabhuni, Chandra Shaker Pittala, Vijay Vallabhuni, Suneetha Bobbillapati, and Bhavani Naga Prasanna, H., "Retinal Vascular Disease Detection from Retinal Fundus Images Using Machine Learning," Australian Patent AU 2020101450. 12 Aug. 2020.

- [35] Rajeev Ratna Vallabhuni, D.V.L. Sravya, M. Sree Shalini, and G. Uma Maheshwararao, "Design of Comparator using 18nm FinFET Technology for Analog to Digital Converters," 2020 7th International Conference on Smart Structures and Systems (ICSSS), Chennai, India, 23-24 july, 2020, pp. 318-323.

- [36] Vallabhuni Rajeev Ratna, M. Saritha, Saipreethi. N, V. Vijay, P. Chandra Shaker, M. Divya, and Shaik Sadulla, "High Speed Energy Efficient Multiplier Using 20nm FinFET Technology," Proceedings of the International Conference on IoT Based Control Networks and Intelligent Systems (ICIC-NIS 2020), Palai, India, December 10-11, 2020, pp. 434-443. Available at SSRN: https://ssrn.com/abstract=3769235 or http://dx.doi.org/10.2139/ssrn.3769235

- [37] Vijay, Vallabhuni, M. Sreevani, E. Mani Rekha, K. Moses, Chandra S. Pittala, KA Sadulla Shaik, C. Koteshwaramma, R. Jashwanth Sai, and Rajeev R. Vallabhuni, "A Review On N-Bit Ripple-Carry Adder, Carry-Select Adder And Carry-Skip Adder," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 27-32.

- [38] Vijay, Vallabhuni, Chandra S. Pittala, A. Usha Rani, Sadulla Shaik, M. V. Saranya, B. Vinod Kumar, RES Praveen Kumar, and Rajeev R. Vallabhuni, "Implementation of Fundamental Modules Using Quantum Dot Cellular Automata," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 12-19.

- [39] Vijay, Vallabhuni, Chandra S. Pittala, K. C. Koteshwaramma, A. Sadulla Shaik, Kancharapu Chaitanya, Shiva G. Birru, Soma R. Medapalli, and Varun R. Thoranala, "Design of Unbalanced Ternary Logic Gates and Arithmetic Circuits," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 20-26.

- [40] Bandi Mary Sowbhagya Rani, Vasumathi Devi Majety, Chandra Shaker Pittala, Vallabhuni Vijay, Kanumalli Satya Sandeep, Siripuri Kiran, "Road Identification Through Efficient Edge Segmentation Based on Morphological Operations," Traitement du Signal, vol. 38, no. 5, Oct. 2021, pp. 1503-1508.

- [41] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Optimal design of VLSI implemented Viterbi decoding," National conference on Recent Advances in Communications & Energy Systems, (RACES-2011), Vadlamudi, India, December 5, 2011, pp. 67-71.

- [42] Katikala Hima Bindu, Sadulla Shaik, V. Vijay, "FINFET Technology in Biomedical-Cochlear Implant Application," International Web Conference on Innovations in Communication and Computing, ICICC '20, India, October 5, 2020.

- [43] Vallabhuni Vijay, and Avireni Srinivasulu, "A Novel Square Wave Generator Using Second Generation Differential Current Conveyor," Arabian Journal for Science and Engineering, vol. 42, iss. 12, 2017, pp. 4983-4990.