WWW.VLSIJOURNAL.COM

# Universal Shift Register: QCA based Novel Technique for Memory Storage Modules

Sungho Jeon<sup>1</sup>, Hyunjae Lee<sup>2</sup>, Hee-Seob Kim<sup>3</sup>, Yeonjin Kim<sup>4</sup>

1-4Department of Electrical and Computer Engineering, Seoul National University, Seoul 08826, Korea

**KEYWORDS:**

QCA; QCA Designer Tool; D flip-flop; 2 to 1 Mux; USR.

ARTICLE HISTORY:

Received 18.07.2022 Accepted 11.08.2022 Published 27.09.2022

DOI: https://doi.org/10.31838/jvcs/05.02.03

#### **Abstract**

A Quantum-dot cellular automaton (QCA) represents a modern technology for implementing small-sized circuits with high-performance, low-power consumption and various computations in digital circuits at the nanoscale level. These quantum dots made up at a nanoscale level which increases the performance of circuits. With the invention of QCA in electronics, the circuits can achieve their operations with very high efficiency and with low power dissipation. Meanwhile, a universal shift register (USR) is a particular circuit with the functions of storing and shifting bits to a specified direction and is observed as an essential component. This USR also has the process to load the data. Therefore, here we propose a USR circuit based on QCA, i.e., QUSR, which requires the essential components of a shift register and a multiplexer (Mux) combined and used to select the operation of the USR. In this project, we propose a 2-to-1 Mux, which then extended to a 4-to-1 Mux. Here, we suggest a new D flip-flop and design a shift register by connecting all of these. Finally, we propose a QUSR that consumes low power and computes high-performance by combining four 4-to-1 Muxes and a four-bit shift register. The proposed QUSR is highly efficient in time and space complexities and has a good energy dissipation performance. The proposed design performance metric of efficiency achieved by doing required simulations using the QCA Designer tool.

Author's e-mail: Jeon.sun@snu.ac.kr, jyunjae.le@snu.ac.kr, h.s.kim@snu.ac.kr, kim. yeonj@snu.ac.kr

How to cite this article: Jeon S, Lee H, Kim H, Kim Y. Universal Shift Register: QCA based Novel Technique for Memory Storage Modules. Journal of Complementary Research, Vol. 5, No. 2, 2023 (pp. 15-21).

## INTRODUCTION

According to Moore's law, the count of transistors and other electronic components on the chip are rapidly increasing using very large-scale integration (VLSI) technology. As a result, it is that much not easy to increase further the count of electronic components in establishing VLSI components. Since more electronic components may increase the size of the chip and increase the temperature inside the chip, that results in damage to the chip.<sup>[1-12]</sup>

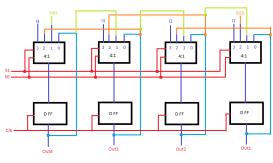

The QCA performs highly dense computing, realized in various material systems; thus, it becomes an alternative to VLSI. In conventional digital systems, the information is transferred from one place to other through electrical current, while in QCA, cells transmit information by propagating a polarization state. So, we introduced QCA technology; in this technology, quantum dots intended to replace the traditional transistor technology, which continues to occupy massive space despite continuous breakthroughs in VLSI technology. The minimization of power dissipation has also entered a stalemate. Hence it is imperative to search for their alternative QCA technology introduced into the picture to establish USR with four D flip-flops and four 4 to 1 Mux connected, as shown in fig1. We Implemented and evaluated this USR in parallel-inparallel-out mode and verified the results.<sup>[13-28]</sup>

# ABOUT QCA

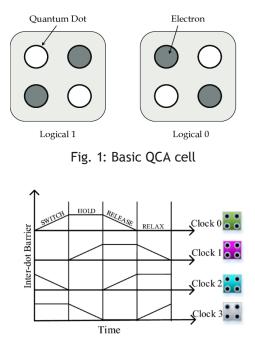

Quantum-dot Cellular Automata (QCA) is a nano technology that John Von Neumann introduced. It consists of a uniform grid of cells, and each consists of four dots assigned with Quantum Dots and electrons together. There are two states named +1 and -1 (Logic 1 and Logic 0). This uniform grid of cells connected in a series called an "Array of cells" or "Quantum wire" transmits an equal amount of energy from beginning to end.<sup>[29-37]</sup> As propagating through cells, the state logic of each cell logic carried to the next adjacent cell in a row. If it passes as diagonal, then it changes its state to +1 to -1 or vice versa. To implement this QUSR, we have QCA Designer Tool software in which at first we implemented basic gates (optional), D flip-flop, and 2 to 1 Mux. The 2 to 1 Mux then extended to 4 to 1 Mux. Moreover, by making a copy of each of the circuit four times, the connection is made. Then, we had implemented our project 4-bit QUSR model, and the results are verified.

Furthermore, the tool also contains four clock signals to give better results as outcomes—the phase of the fourth pulse changes opposite to the first clock pulse. Moreover, it includes two simulation engine types, namely Bistable Approximation Simulation and Coherence Vector Simulation (Fig. 2).

## **BASIC GATES**

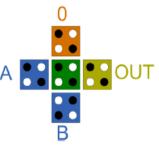

Basic gates such as "AND" gate, "OR" gate, "NOT" gate are designed and implemented using QCA Designer Tool. AND gate (Table 1 and Fig. 3):

$$OUT = A.B$$

(1)

Fig. 2: Phases of clock signals in QCA

| Table I. Truth table of AND Gate |   |     |  |

|----------------------------------|---|-----|--|

| A                                | В | OUT |  |

| 0                                | 0 | 0   |  |

| 0                                | 1 | 0   |  |

| 1                                | 0 | 0   |  |

| 1                                | 1 | 1   |  |

#### OR gate (Table 2 and Fig. 4)

$$OUT = A + B \tag{2}$$

#### NOT gate (Table 3 and Fig. 5)

$$A_{bar} = not(A)$$

(3)

The above three are basic gates designed and implemented using the QCA Designer tool and verified the simulation results with the following truth tables.

#### **PROPOSED MODELS**

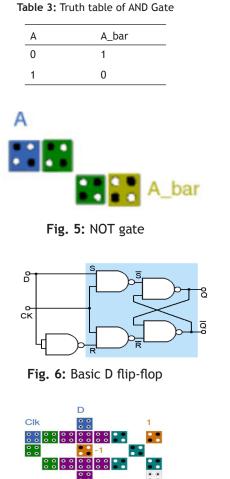

#### Implementation of D Flip-Flop

D flip-flop is a digital electronic circuit, and it used to delay the change of state of its output signal until the next rising edge of a clock timing input signal occurs. The D flip-flop is essential, and it gives the solution when SR inputs have high logic, and the output may be forbidden. Introduction of an inverter in between the inputs of SR flip-flop and allows a single input D to overcome that situation.

The QCA with four clocking zones is used to implement a D flip-flop. The proposed D flip-flop using QCA technology

Fig. 3: AND gate

Table 2. Truth table of OR Gate

| Α | В | OUT |  |

|---|---|-----|--|

| 0 | 0 | 0   |  |

| 0 | 1 | 1   |  |

| 1 | 0 | 1   |  |

| 1 | 1 | 1   |  |

Journal of VLSI circuits and systems, , ISSN 2582-1458

16

implemented in the QCA Designer tool shown in Figure 7, which produces the equal outputs as basic D flip-flop generates. The parallel input parallel output of QUSR designed using this D flip-flop (Table 4).

The series combination of four D flip-flops used to implement this proposed QUSR. It has four parallel data inputs from D1 to D4 and four similar outputs, Out1 to Out4. When we gave the four inputs and also clocked input simultaneously, the outputs also get simultaneously.

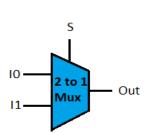

## Implementation of 2 to 1 Mux

The multiplexer, in short MUX, is a combinational logic circuit designed to switch one of the several input lines to a single standard output line using the control signal/ select signal. Therefore, the select line acts as a rotary

switch when it OFF (logic 0), picks one as output, and when it ON (logic 1), it picks another as output. Therefore, MUX operates like fast-acting multiple position rotatory switches connecting and controlling numerous channels/ input lines.

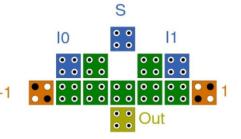

It consists of two inputs which are I0 and I1, and one select line S, for which the select signal selects the input signal to flow through an output Out, which means the output is connected to any of the inputs depending on the select signal. This circuit mainly used in discrete signals in which, from the specified signal chosen, the outcome connected to selected inputs. That implies at one instant of time, and it selects only one input to flow through output.

The proposed 2 to 1 Mux using QCA technology implemented in the QCA Designer tool shown in Figure 9, which produces the equal outputs as basic 2 to 1 Mux generates.

Fig. 8: Proposed D flip-flop

| Table IV: D flip-flop truth table |   |        |  |

|-----------------------------------|---|--------|--|

| Clk D Out                         |   |        |  |

| 0                                 | Х | Memory |  |

| 1                                 | 0 | 0      |  |

| 1                                 | 1 | 1      |  |

|                                   |   |        |  |

Fig. 9: Basic 2 to 1 Mux block

Fig. 10: Proposed 2 to 1 Mux

| Table 5: 2 to 1 Mux truth table |     |  |

|---------------------------------|-----|--|

| S                               | Out |  |

| 0                               | 10  |  |

| 1                               | l1  |  |

Fig. 11: Proposed 4 to 1 Mux

Journal of VLSI circuits and systems, , ISSN 2582-1458

## Implementation of 4 to 1 Mux from 2 to 1 Mux

By using three 2 to 1 mux's, we had designed one 4 to 1 mux. For that, we must require three 2 to 1 mux's to that four inputs and two select signals; based on the selected signals, the output connected to corresponding input signals. In this instance, only one of four inputs is connected to the output, which can be achieved by selected lines S1 and S0 act as a rotatory switch to produce the desired output response. The proposed 4 to 1 mux is shown in fig.10 and verified the results from the truth table given below table 3.

This 4 to 1 mux has two selected lines, namely S1 and S0, which indicates the output to connect for the specified input. Thus, 4 to 1 Mux acts as a four input and one output selector circuit, selecting the required operation to perform in our project.

## **Implementation of USR**

Universal Shift Register (USR) is a register used to store and shift the bits of the data in the required directions with parallel load capability. It can also be used to perform input and output operations in both serial and parallel operations. The unidirectional and bidirectional shift register are combined to get the design of the USR. A USR has both shift-right and shift-left signals; they are used to move the data according to the given input information. When shift left operation is performed, the data transfer shift towards the left in the serial path; similarly, when shift right operation is performed, the data transfer shift towards the right in the serial direction. When parallel load operation is performed, then data stored in parallel and gets output in parallel. Hence the USR can do both input and output operations with both serial and parallel loads. In this project, we are implementing a parallel-inparallel-out universal shift register. That means we are

| Table 6: 4 to 1 mux truth table |    |     |  |

|---------------------------------|----|-----|--|

| S1                              | SO | Out |  |

| 0                               | 0  | 10  |  |

| 0                               | 1  | 11  |  |

| 1                               | 0  | 12  |  |

| 1                               | 1  | 13  |  |

Fig. 12: Block diagram of USR

operating the USR to perform parallel loading and parallel retrieving of the data.

Our proposed USR contains four input signals, one shiftleft signal and one shift-right signal; based on the selected signals, the required operation performed. Moreover, it can be used for loading data and retrieving data of concerned clock signals. From the below basic block diagram, we can observe how a USR works.

#### Operation

When select lines S1 and S0 are logic low, then "0" of each Mux selected as output in Mux that carried to D flipflop, and it again connected to "0" of the next Mux and continuous. That means the means data is unchanged.

When select line S1 is low, and S2 is high, then "1" of each Mux selected, which means shift right operation performed, the output of every D flip-flop connected to the next Mux. That results in shifting the data in the right direction.

When select line S1 is high, and S2 is low, then "2" of each Mux selected, which means shift left operation performed, the output of every D flip-flop connected to the previous Mux. That results in shifting the data in the left direction.

When select line S1 and S0 are logic high, then "3" of each Mux selected results in parallel loading of data; the same output of each Mux given as input to every D flipflop. Then the main aim of our project that is parallel-inparallel-out, is achieved.

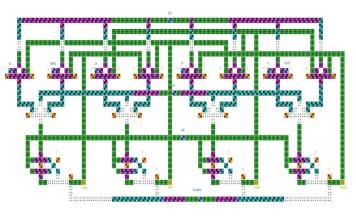

The figure 13 is the USR of QCA technology designed using the QCA Designer tool, which performs the

Table 7: USR Operation for specifically selected inputs

| 51 | SO | Output        |

|----|----|---------------|

| 0  | 0  | Unchanged     |

| 0  | 1  | Shift-Right   |

| 1  | 0  | Shift-Left    |

| 1  | 1  | Parallel Load |

Fig. 13: Proposed USR using QCA Technology in QCA Designer Tool

operations of the primary Universal Shift Register. To load data in parallel-in-parallel-out form, store data, and shift the data by specified direction. In this circuit, enable is always high that clears each flip-flop results and each clock signal. A clock signal deployed to perform memory storage in the flip-flop. S0 and S1 used as selected lines, and this circuit is a four-bit USR, so four inputs are given to "4" of each Mux.

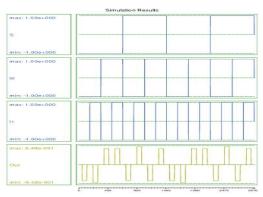

# SIMULATION RESULTS

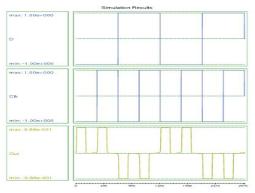

Figure 13 represents the simulation of a D flip-flop that states when CLK is logic high, and then it gives D has output; else it gives logic low has output. Figure 14 represents a 2 to 1 MUX simulation, which states when

Fig. 14: D Flip-Flop QCA Simulation

Figure14. Mux 2 to1 QCA Simulation.

Figure15. Mux 4 to 1 QCA Simulation.

| Table 5: Existing vs Proposed mode | sting vs Proposed model |

|------------------------------------|-------------------------|

|------------------------------------|-------------------------|

| Case              | Existing Model | Proposed Model |

|-------------------|----------------|----------------|

| Efficiency        | Medium         | High           |

| Performance       | Slow           | Fast           |

| Complexity        | Hard           | Simple         |

| Power consumption | More           | Low            |

select line S handles the input to go through the output. Figure 15 represents a 4 to 1 MUX simulation that states depending on the selected line S1 and S0; the output gets from the given inputs.

The table 5 states that this proposed model of USR has many advantages compared to the existing model in the field of electronics. The parameters like efficiency, performance increases and complexity and power consumption decrease by using QCA technology. Therefore, USR designed and implemented using the QCA Designer tool application.

# CONCLUSION

The USR designed using QCA technology on the QCA Designer tool to store and shift data in both directions (left and right) using a D flip-flop and 4 to 1 Mux. That helps to minimize power consumption and increase its performance compared with the existing model, VLSI technology. This kind of USR implemented with the help of nanotechnology, and then it evacuates the VLSI in creating chips with transistors and other electronic devices in the design of USR. That can be done when nanotechnology comes into the electronic field; then, many inventions may be made and improve this project and be applied to get product-type results. From the obtained results obtained, we can conclude that by using the QCA Designer tool, we can design USR by using QCA technology and can operate in parallel-in-parallel-out mode and make efficient and has fast response when compared to the VLSI model of USR.

# REFERENCES

- [1] Dr. S. Selvakanmani, Mr. Rajeev Ratna Vallabhuni, Ms. B. Usha Rani, Ms. A. Praneetha, Dr. Urlam Devee Prasan, Dr. Gali Nageswara Rao, Ms. Keerthika. K, Dr. Tarun Kumar, Dr. R. Senthil Kumaran, Mr. Prabakaran.D, "A Novel Global Secure Management System with Smart Card for IoT and Cloud Computing," The Patent Office Journal No. 06/2021, India. International classification: H04L29/08. Application No. 202141000635 A.

- [2] Nalajala Lakshman Pratap, Rajeev Ratna Vallabhuni, K. Ramesh Babu, K. Sravani, Bhagyanagar Krishna Kumar, Angothu Srikanth, Pijush Dutta, Swarajya Lakshmi V Papineni, Nupur Biswas, K.V.S.N.Sai Krishna Mohan, "A Novel Method of Effective Sentiment Analysis System by Improved Relevance Vector Machine," Australian Patent AU 2020104414. 31 Dec. 2020

- [3] S.V.S Prasad, Chandra Shaker Pittala, V. Vijay, and Rajeev Ratna Vallabhuni, "Complex Filter Design for Bluetooth Receiver Application," In 2021 6th International Conference on Communication and Electronics Systems (ICCES), Coimbatore, India, July 8-10, 2021, pp. 442-446.

- [4] Chandra Shaker Pittala, J. Sravana, G. Ajitha, P. Saritha, Mohammad Khadir, V. Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Novel Methodology to Validate DUTs Using Single Access Structure," 5th International Conference on Electronics, Materials Engineering and Nano-Technology (IEMENTech 2021), Kolkata, India, September 24-25, 2021, pp. 1-5.

- [5] Chandra Shaker Pittala, M. Lavanya, V. Vijay, Y.V.J.C. Reddy, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Energy Efficient Decoder Circuit Using Source Biasing Technique in CNTFET Technology," 2021 Devices for Integrated Circuit (DevIC), Kalyani, India, May 19-20, 2021, pp. 610-615.

- [6] Chandra Shaker Pittala, M. Lavanya, M. Saritha, V. Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Biasing Techniques: Validation of 3 to 8 Decoder Modules Using 18nm FinFET Nodes," 2021 2nd International Conference for Emerging Technology (INCET), Belagavi, India, May 21-23, 2021, pp. 1-4.

- [7] P. Ashok Babu, V. Siva Nagaraju, Ramya Mariserla, and Rajeev Ratna Vallabhuni, "Realization of 8 x 4 Barrel shifter with 4-bit binary to Gray converter using FinFET for Low Power Digital Applications," Journal of Physics: Conference Series, vol. 1714, no. 1, p. 012028. IOP Publishing. doi:10.1088/1742-6596/1714/1/012028

- [8] Vallabhuni Vijay, C. V. Sai Kumar Reddy, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, M. Saritha, M. Lavanya, S. China Venkateswarlu and M. Sreevani, "ECG Performance Validation Using Operational Transconductance Amplifier with Bias Current," International Journal of System Assurance Engineering and Management, vol. 12, iss. 6, 2021, pp. 1173-1179.

- [9] Vallabhuni, Rajeev Ratna, M. Saritha, Sruthi Chikkapally, Vallabhuni Vijay, Chandra Shaker Pittala, and Sadulla Shaik, "Universal Shift Register Designed at Low Supply Voltages in 15 nm CNTFET Using Multiplexer," In International Conference on Emerging Applications of Information Technology, pp. 597-605. Springer, Singapore, 2021.

- [10] B. M. S. Rani, Vallabhuni Rajeev Ratna, V. Prasanna Srinivasan, S. Thenmalar, and R. Kanimozhi, "Disease prediction based retinal segmentation using bi-directional ConvLSTMU-Net," Journal of Ambient Intelligence and Humanized Computing, 2021, pp. 1-10. https://doi. org/10.1007/s12652-021-03017-y

- [11] Rajeev Ratna Vallabhuni, A. Karthik, CH. V. Sai Kumar, B. Varun, P. Veerendra, and Srisailam Nayak, "Comparative Analysis of 8-Bit Manchester Carry Chain Adder Using FinFET at 18nm Technology," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), Thoothukudi, India, 2020, pp. 1579-1583, doi: 10.1109/ ICISS49785.2020.9316061.

- [12] R. R. Vallabhuni, P. Shruthi, G. Kavya and S. Siri Chandana, "6Transistor SRAM Cell designed using 18nm FinFET Technology," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), Thoothukudi, India, 2020, pp. 1584-1589, doi: 10.1109/ICISS49785.2020.9315929.

- [13] Rajeev Ratna Vallabhuni, J. Sravana, M. Saikumar, M. Sai Sriharsha, and D. Roja Rani, "An advanced computing architecture for binary to thermometer decoder using 18nm FinFET," 2020 Third International Conference on Smart Systems and Inventive Technology (ICSSIT), Tirunelveli, India, 20-22 August, 2020, pp. 510-515.

- [14] Rajeev Ratna Vallabhuni, K.C. Koteswaramma, B. Sadgurbabu, and Gowthamireddy A, "Comparative Validation of SRAM Cells Designed using 18nm FinFET for Memory Storing Applications," Proceedings of the 2nd International Conference on IoT, Social, Mobile, Analytics & Cloud in Computational Vision & Bio-Engineering (ISMAC-CVB 2020), 2020, pp. 1-10.

- [15] V. Siva Nagaraju, Rapaka Anusha, and Rajeev Ratna Vallabhuni, "A Hybrid PAPR Reduction Technique in OFDM Systems," 2020 IEEE International Women in Engineering (WIE) Conference on Electrical and Computer Engineering (WIECON-ECE), Bhubaneswar, India, 26-27 Dec. 2020, pp. 364-367.

- [16] V. Siva Nagaraju, P. Ashok babu, B. Sadgurbabu, and Rajeev Ratna Vallabhuni, "Design and Implementation of Low power FinFET based Compressor," 2021 3rd International Conference on Signal Processing and Communication (ICP-SC), Coimbatore, India, 13-14 May 2021, pp. 532-536.

- [17] P. Ashok Babu, V. Siva Nagaraju, and Rajeev Ratna Vallabhuni, "Speech Emotion Recognition System With Librosa," 2021 10th IEEE International Conference on Communication Systems and Network Technologies (CSNT), Bhopal, India, 18-19 June 2021, pp. 421-424.

- [18] P. Ashok Babu, V. Siva Nagaraju, and Rajeev Ratna Vallabhuni, "8-Bit Carry Look Ahead Adder Using MGDI Technique," IoT and Analytics for Sensor Networks, Springer, Singapore, 2022, pp. 243-253.

- [19] Rajeev Ratna Vallabhuni, Jujavarapu Sravana, Chandra Shaker Pittala, Mikkili Divya, B.M.S.Rani, and Vallabhuni Vijcaay, "Universal Shift Register Designed at Low Supply Voltages in 20nm FinFET Using Multiplexer," In Intelligent Sustainable Systems, pp. 203-212. Springer, Singapore, 2022.

- [20] P. Chandra Shaker, V. Parameswaran, M. Srikanth, V. Vijay, V. Siva Nagaraju, S.C. Venkateswarlu, Sadulla Shaik, and Vallabhuni Rajeev Ratna, "Realization and Comparative analysis of Thermometer code based 4-Bit Encoder using 18nm FinFET Technology for Analog to Digital Converters," In: Reddy V.S., Prasad V.K., Wang J., Reddy K.T.V. (eds) Soft Computing and Signal Processing. Advances in Intelligent Systems and Computing, vol 1325. Springer, Singapore. https://doi.org/10.1007/978-981-33-6912-2\_50

- [21] Rajeev Ratna Vallabhuni, G. Yamini, T. Vinitha, and S. Sanath Reddy, "Performance analysis: D-Latch modules designed using 18nm FinFET Technology," 2020 International Conference on Smart Electronics and Communication (ICOSEC), Tholurpatti, India, 10-12, September 2020, pp. 1171-1176.

- [22] Rani, B.M.S, Divyasree Mikkili, Rajeev Ratna Vallabhuni, Chandra Shaker Pittala, Vijay Vallabhuni, Suneetha Bobbillapati, and Bhavani Naga Prasanna, H., "Retinal Vascular Disease Detection from Retinal Fundus Images Using Machine Learning," Australian Patent AU 2020101450. 12 Aug. 2020.

20

- [23] Rajeev Ratna Vallabhuni, D.V.L. Sravya, M. Sree Shalini, and G. Uma Maheshwararao, "Design of Comparator using 18nm FinFET Technology for Analog to Digital Converters," 2020 7th International Conference on Smart Structures and Systems (ICSSS), Chennai, India, 23-24 july, 2020, pp. 318-323.

- [24] Vallabhuni Rajeev Ratna, M. Saritha, Saipreethi. N, V. Vijay, P. Chandra Shaker, M. Divya, and Shaik Sadulla, "High Speed Energy Efficient Multiplier Using 20nm FinFET Technology," Proceedings of the International Conference on IoT Based Control Networks and Intelligent Systems (ICIC-NIS 2020), Palai, India, December 10-11, 2020, pp. 434-443. Available at SSRN: https://ssrn.com/abstract=3769235 or http://dx.doi.org/10.2139/ssrn.3769235

- [25] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Optimal design of VLSI implemented Viterbi decoding," National conference on Recent Advances in Communications & Energy Systems, (RACES-2011), Vadlamudi, India, December 5, 2011, pp. 67-71.

- [26] Katikala Hima Bindu, Sadulla Shaik, V. Vijay, "FINFET Technology in Biomedical-Cochlear Implant Application," International Web Conference on Innovations in Communication and Computing, ICICC '20, India, October 5, 2020.

- [27] V. Vijay, J. Prathiba, S. Niranjan Reddy, V. Raghavendra Rao, "Energy efficient CMOS Full-Adder Designed with TSMC 0.18µm Technology," International Conference on Technology and Management (ICTM-2011), Hyderabad, India, June 8-10, 2011, pp. 356-361.

- [28] Vallabhuni Vijay, Pittala Chandra shekar, Shaik Sadulla, Putta Manoja, Rallabhandy Abhinaya, Merugu rachana, and Nakka nikhil, "Design and performance evaluation of energy efficient 8-bit ALU at ultra low supply voltages using FinFET with 20nm Technology," VLSI Architecture for Signal, Speech, and Image Processing, edited by Durgesh Nandan, Basant Kumar Mohanty, Sanjeev Kumar, Rajeev Kumar Arya, CRC press, 2021.

- [29] Rajeev Ratna Vallabhuni, S. Lakshmanachari, G. Avanthi, and Vallabhuni Vijay, "Smart Cart Shopping System with an RFID Interface for Human Assistance," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), Thoothukudi, India, 2020, pp. 165-169, doi: 10.1109/ICISS49785.2020.9316102.

- [30] Saritha, M., Kancharapu Chaitanya, Vallabhuni Vijay, Adam Aishwarya, Hasmitha Yadav, and G. Durga Prasad, "Adaptive And Recursive Vedic Karatsuba Multiplier Using Non Linear Carry Select Adder," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 22-29.

- [31] Vijay, Vallabhuni, Kancharapu Chaitanya, Chandra Shaker Pittala, S. Susri Susmitha, J. Tanusha, S. China Venkateshwarlu, and Rajeev Ratna Vallabhuni, "Physically Unclonable Functions Using Two-Level Finite State Machine," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 33-41.

- [32] Vijay, Vallabhuni, M. Sreevani, E. Mani Rekha, K. Moses, Chandra S. Pittala, KA Sadulla Shaik, C. Koteshwaramma, R. Jashwanth Sai, and Rajeev R. Vallabhuni, "A Review On N-Bit Ripple-Carry Adder, Carry-Select Adder And Carry-Skip Adder," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 27-32.

- [33] Vijay, Vallabhuni, Chandra S. Pittala, A. Usha Rani, Sadulla Shaik, M. V. Saranya, B. Vinod Kumar, RES Praveen Kumar, and Rajeev R. Vallabhuni, "Implementation of Fundamental Modules Using Quantum Dot Cellular Automata," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 12-19.

- [34] Vijay, Vallabhuni, Chandra S. Pittala, K. C. Koteshwaramma, A. Sadulla Shaik, Kancharapu Chaitanya, Shiva G. Birru, Soma R. Medapalli, and Varun R. Thoranala, "Design of Unbalanced Ternary Logic Gates and Arithmetic Circuits," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 20-26.

- [35] Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, Vallabhuni Vijay, Usha Rani Anam, Kancharapu Chaitanya, "Numerical analysis of various plasmonic MIM/MDM slot waveguide structures," International Journal of System Assurance Engineering and Management, 2022.

- [36] M. Saritha, M. Lavanya, G. Ajitha, Mulinti Narendra Reddy, P. Annapurna, M. Sreevani, S. Swathi, S. Sushma, Vallabhuni Vijay, "A VLSI design of clock gated technique based ADC lock-in amplifier," International Journal of System Assurance Engineering and Management, 2022, pp. 1-8. https://doi.org/10.1007/s13198-022-01747-6

- [37] Chandra Shaker Pittala, Vallabhuni Vijay, B. Naresh Kumar Reddy, "1-Bit FinFET Carry Cells for Low Voltage High-Speed Digital Signal Processing Applications," Silicon, 2022. https://doi.org/10.1007/s12633-022-02016-8.

- [38] Vallabhuni Vijay, Kancharapu Chaitanya, T. Sai Jaideep, D. Radha Krishna Koushik, B. Sai Venumadhav, Rajeev Ratna Vallabhuni, "Design of Optimum Multiplexer In Quantum-Dot Cellular Automata," International Conference on Innovative Computing, Intelligent Communication and Smart Electrical systems (ICSES -2021), Chennai, India, September 24-25, 2021.

- [39] S. China Venkateswarlu, N. Uday Kumar, D. Veeraswamy, and Vallabhuni Vijay, "Speech Intelligibility Quality in Telugu Speech Patterns Using a Wavelet-Based Hybrid Threshold Transform Method," International Conference on Intelligent Systems & Sustainable Computing (ICISSC 2021), Hyderabad, India, September 24-25, 2021.

- [40] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Low power based optimal design for FPGA implemented VMFU with equipped SPST technique," National Conference on Emerging Trends in Engineering Application (NCE-TEA-2011), India, June 18, 2011, pp. 224-227.

- [41] S. China Venkateswarlu, Ch. Sashi Kiran, R.V. Santhosh Nayan, Vijay Vallabhuni, P. Ashok Babu, V. Siva Nagaraju, "Artificial Intelligence Based Smart Home Automation System Using Internet of Things," The Patent Office Journal No. 09/2021, India. Application No. 202041057023 A.

- [42] Bandi Mary Sowbhagya Rani, Vasumathi Devi Majety, Chandra Shaker Pittala, Vallabhuni Vijay, Kanumalli Satya Sandeep, Siripuri Kiran, "Road Identification Through Efficient Edge Segmentation Based on Morphological Operations," Traitement du Signal, vol. 38, no. 5, Oct. 2021, pp. 1503-1508.

- [43] Vallabhuni Vijay, and Avireni Srinivasulu, "A Novel Square Wave Generator Using Second Generation Differential Current Conveyor," Arabian Journal for Science and Engineering, vol. 42, iss. 12, 2017, pp. 4983-4990.