# Thermometer Coding-Based Application-Specific Efficient Mod Adder for Residue Number Systems

### <sup>1,2</sup>K. Vijaya Vardhan,<sup>3</sup>Sarada Musala

<sup>1</sup>Department of ECE, Vignan's Foundation for Science, Technology and Research, Guntur, Andhra Pradesh, India 522213 <sup>2</sup>Department of ECE, Vignan's LARA Institute of Technology & Science, Guntur, Andhra Pradesh, India522213 <sup>3</sup>Department of ECE, Vignan's Foundation for Science, Technology and Research, Guntur, Andhra Pradesh, India 522213

KEYWORDS: RNS, TCR, Modular Adder, Forward and Reverse Converters.

ARTICLE HISTORY: Submitted : 15.11.2021 Revised : 12.01.2023

Revised : 12.01.2023 Accepted : 26.11.2024

### ABSTRACT

The interest of researchers in the implementation of power-efficient digital circuits has drastically increased in the last few decades. The reason for this is that most of the applications like Embedded Systems, Communications, Digital Signal Processing, etc., are battery-operated and in some applications, it is impossible to give a conventional power supply connection. In recent years, a substitution for the conventional number system is the Residue Number System (RNS). RNS systems are efficient in terms of power, area, speed, etc. The power consumption of the circuit depends on several factors, one factor is how fast the circuit can perform the operations. In most digital applications adders play a crucial role. A novel mod adder based on Thermometer coding has been proposed, which yields superior results in comparison to the current state-of-the-art methods. The suggested addition process was designed by using thermometer coding. The proposed adder was simulated by using the NC launch tool in the Cadence.

Author e-mail: kvvardhan405@gmail.com,Sarada.marasu@gmail.com

How to cite this article: Vardhan VK, Musala S. Thermometer Coding-Based Application-Specific Efficient Mod Adder for Residue Number Systems, Journal of VLSI Circuits and System Vol. 6, No. 2, 2024 (pp. 122-129).

https://doi.org/10.31838/jvcs/06.02.14

### Introduction

Modern technology Enhancing energy efficiency is necessary for Deep Learning,<sup>[1]</sup> DSP,<sup>[2]</sup> and the Internet of Things.<sup>[3]</sup> With the use of arithmetic and conventional number systems, efficient embedded systems (ES) have recently been created, and their performance has been enhanced.<sup>[2]</sup> Applications such as Digital Signal Processing (DSP),<sup>[4]</sup> Cryptography,<sup>[5]</sup> and Residue Number System (RNS)<sup>[6]</sup> are employed to perform highspeed, fault-tolerant, and low-power calculations. Add and multiply are commonly used in the majority of RNS operations, such as add, subtract, divide, scaling, forward and reverse conversions.<sup>[2]</sup>. The conventional data is converted into residue data this process is called Forward Conversion. Similarly, residue data is converted into conventional data is called Reverse conversion. The second one is more difficult than the first conversion.

The unary coding, in which the size of the number is determined by the number of 1s it contains, is commonly used in thermometer coding (TC). One application of Golomb coding is in data compacting in neural networks.<sup>[7-8]</sup> One of the subclasses of Golomb coding is TC. Thermo-

Journal of VLSI circuits and systems, , ISSN 2582-1458

meter coding (TC) is a straightforward technique for enhancing the performance of RNS computing components, such as modular multipliers, subtractors, and adders.<sup>[9]</sup>

Engineers and researchers are becoming more interested in the design of modular adders that use TC.<sup>[10]</sup> It is legal to translate equivalent residues in TC format from analog inputs using current ADCs.[11] By adding TC numbers in RNS, one can add compact moduli faster than in traditional processes because there is no carry propagation involved. Forward converters are not needed for TC number addition because ADCs are employed to encode the input TC numbers.<sup>[11]</sup> Effective RNS systems require the selection of modest moduli. Applications in the form of embedded low-power devices and Internet of Things devices Thermometer Coding-based mod adders are appropriate since adders need a limited dynamic range.<sup>[2]</sup> Among the first unweighted number systems was RNS. One intrinsic feature of RNS is its capacity to do simple arithmetic operations, where the outcome of each numerical position is determined by the number that exists at that location. The moduli set is denoted

as  $\{p_1, p_2, ..., p_n\}$ , where 'p<sub>i</sub>' represents the value of the ith modulus. The RNS is typically depicted as a collection of suitably chosen prime numbers referred to as the moduli.<sup>[12]</sup>

Residue Number System (RNS) represents each 'K' number as a collection of smaller numbers called residues. The value of each residue, designated by the symbol 'r<sub>i</sub>', corresponds to the ith position. The residue 'r<sub>i</sub>' is defined as the remainder obtained when 'K' is divided by the modulus value 'p<sub>i</sub>' such that the remainder is minimized. In technical terms, the relationship might be characterized as,

Every integer 'K' that falls under the 'Dynamic Range (DR)' of RNS and is expressly expressed in it. The Dynamic Range is represented as the set of moduli  $\{p_1, p_2, ..., p_n\}$ , denoted as 'L'.

$$L=\prod_{i=1}^{n} m_{i}$$

(2)

All integers in the interval '0' to 'L-1' have explicit definitions in RNS. After that, a number may develop similarly.<sup>[13]</sup>

Mod addition between two residue numbers U and  $V^{\mbox{\scriptsize [14]}}$  as follows

$$T = U + V = (t_n, t_{n-1}, ..., t_1)$$

(3)

With

$$t_{i} = \begin{cases} u_{i} + v_{i} & if u_{i} + v_{i} < m_{i} \\ u_{i} + v_{i} - m_{i} & if u_{i} + v_{i} \ge m_{i} \end{cases}$$

(4)

Consider the RNS numbers for the above addition

$$U = (u_n, u_{(n-1)}, \dots, u_1)$$

(5)

$$V = (V_n, V_{(n-1)}, \dots, V_1)$$

(6)

Thermometer Coding (TC) is used in RNS systems, it will be called TCR. By using TC in RNS systems are less power consumption and energy efficient. The TC representation of digits from 0 to 5 by using 6 bits is shown in below Table 1.

In the TC format, the magnitude of the number increases as the number of needed bits increases. Likewise, the numerical value is low, and the number of bits needed is minimal. The number of occurrences of the digit 1 in the number can be positioned in any direction, although for optimal use of TC numbers, it is advisable to place the 1's on the right-hand side.TCRs enable the modular addition of two operands by concatenating and bit-shifting the concatenated augend and addend, then taking the modulo of the intermediate sum to keep the result inside the original length of the modular thermometer residue.

The reverse conversion was carried out using a variety of methods, including the Chinese Remainder Theorem (CRT),<sup>[15-17]</sup> Mixed Radix Conversion (MRC),<sup>[18]</sup> and the New Chinese Remainder Theorem.<sup>[19]</sup> The design of reverse converters heavily relies on mod adders. The CRT methodology is more commonly used than MRC due to its concurrent nature. Adders are designed these days with a variety of methods0<sup>[20], [21]</sup>

| Table 1. | TC represen | tation of | digits | from 0 | ) to 5 |

|----------|-------------|-----------|--------|--------|--------|

|----------|-------------|-----------|--------|--------|--------|

| Decimal Digit | TC Representation |  |  |  |  |

|---------------|-------------------|--|--|--|--|

| 0             | 000000            |  |  |  |  |

| 1             | 000001            |  |  |  |  |

| 2             | 000011            |  |  |  |  |

| 3             | 000111            |  |  |  |  |

| 4             | 001111            |  |  |  |  |

| 5             | 011111            |  |  |  |  |

This study suggests a brand-new modular adder construction based on TCRs. The suggested modular adder consumes less power than the current works,<sup>[11], [22]</sup> which utilize 2X1 MUXs and many logic gates. The addition process was accomplished by using XOR gates.<sup>[23-27]</sup>

The structure of this document is as follows. First discussed the current and TC modular adders. Next discussed the anticipated TC-based mod adder. Later comparison between the proposed design and the existing works are compared. At the end concluded with some findings are discussed.

### LITERATURE

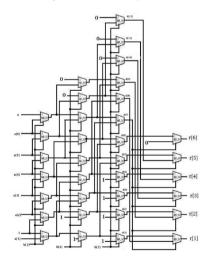

By retaining the distributed arithmetic paradigm, the TCbased modular adders are essential to TC-based modular multiplication.<sup>[14]</sup> Fig. 1 illustrates the design of the Mod 7 thermometer coding-based adder, as per reference.<sup>[21]</sup> One integer is given in binary form as b[1], b[2], & b[3] out of two numbers in the proposed adder. In this case, the positional weights of bits b[1], b[2], and b[3] are 1, 2, and 4, respectively. The first number's 1s should be added to the second (a[6]a[5]a[4]a[3]a[2]a[1]). If the sum of ones in the result exceeds the value of 'm- 1', then the number of beginning ones is subtracted from the sum.

Now, let us analyze an illustration.where the first number (A) is expressed in TC form (a[6]a[5]a[4]a[3]a[2]a[1] =

000111), the second number (B) is stated in binary form 101 (b[1] = 1, b[2] = 0 & b[3] = 1). The least significant binary digit (b[1]) affects the MUXs in the opening stage, moving the first binary digit to the left and adding one to the end of the least significant binary digit (rightmost bit position). If b[2] is '1', the second stage MUXs then move the input two bits to the left before appending two 1s to the end of the least significant bit position. Alternatively, during this phase, the MUXs simply add or shift zero values; they merely move them from the input into the output. The third stage's MUXs transfer inputs at zero to outputs similarly to the second stage. The MUXs in this stage left shift four times and add four ones to the end of the least significant bit position when b[3] is '0' or equal to one.

Therefore, the values of 'D' (d[12]d[11]d[10]d[9]d[8] d[7]d[6]d[5]d[4]d[3]d[2]d[1]) indicate the output of third stage MUXs. These numbers are 000011111111.

Depending on d[7], the adder's output is expressed in a certain way. Bits d[8] to d[12] are obtained via the final MUXs stage if d[7] = '1', indicating that the 'sum  $\ge$  m'. In the last stage, MUXs result in the bits d[1] to d[6] if d[7] = '0', indicating that the sum is less than 'm'. d[7] wasthe selection signal utilized by the final stage MUXs.

Fig.1: TCR-based Mod-7 Adder [21]

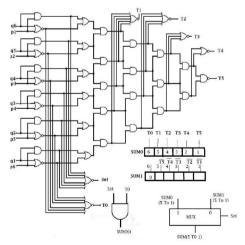

A novel TCR-based modular adder with reduced latency and circuit size was introduced in,<sup>[22]</sup> in contrast to the TC-based adder disclosed in.<sup>[21]</sup> This recommended adder takes TC-formatted inputs. Then, it is determined if 'P + Q  $\ge$  m' or 'P + Q < m' by combining the two residues with moduli 'm'. Before calculating the sum, the bits that indicate the integer 'Q' are reversed. After that, the inputs are put via logical AND & NOR procedures. When an AND gate has at least one output that is 1, the outcome (P + Q  $\ge$  m) occurs. To put it another way, if only one AND gate output is '1', total (P + Q = m) will result in '0'. This keeps on until a couple AND gates generate logic '1', which happens when the output also generates logic '1'. The function P + Q < m can be implemented using the logical gates NOR.

$$Sum = \begin{cases} SUM1, & ifk = 1 \ (P+Q \ge m) \\ SUM0, & ifk = 0 \ (P+Q < m) \end{cases}$$

(7)

where

$$k = \bigvee_{i=1}^{m-1} (p_i \wedge q_{m-i})$$

(8)

$$SUM1 = (\sum_{i=1}^{m-1} p_i \wedge q_{m-i}) - 1$$

(9)

$$SUM0 = (m-1) - \left(\sum_{i=1}^{m-1} \left(\overline{p_i \vee q_{m-i}}\right)\right)$$

(10)

To use the values in arithmetic modulo 'm', P and Q are framed with 'm-1' - bits in TCR.

$$P = p_{m-1} \dots p_2 p_1 = \underbrace{0 \dots 0}_{p_{\text{zeros}}} \underbrace{1 \dots 1}_{p_{\text{ones}}}$$

(11)

$$Q = q_{m-1} \dots q_2 q_1 = \underbrace{0 \dots 0}_{\substack{q \text{ proce}}} \underbrace{1 \dots 1}_{\substack{q \text{ proce}}}$$

(12)

The sum of the bits in  $P_{zeros}$  plus  $P_{ones}$  and  $Q_{zeros}$  plus  $Q_{ones}$ , respectively, in equations (11) and (12) is equal to the (m-1). when faced withindividual occurrences in the input numbers are added together, there's a chance the total will be greater than the mod value and require more storage space than is required. The second number in this case may be interpreted as flipped or reversed. To assess this scenario, the bitwise logical AND operation is performed between the variable 'P' and the complement of variable 'Q'.

$$P = \underbrace{0\dots0}_{p_{\text{zeros}}} \underbrace{1\dots1}_{z} \underbrace{1\dots1}_{p_{\text{ones-z}}}$$

(13)

$$Q_{reverse} = \underbrace{1...1}_{q_{\text{ones-z}}} \underbrace{1...1}_{z} \underbrace{0...0}_{q_{\text{zeros}}}$$

(14)

$$P \wedge Q_{reverse} = \underbrace{0...0}_{p_{zeros}} \underbrace{1...1}_{z} \underbrace{0...0}_{q_{zeros}}$$

(15)

In this instance,  $P + Q \ge m$  (16) because the ones of 'P' and the opposite version of 'Q' overlap. where the number of overlapping 1s is indicated by 'z'.

$$\begin{cases} P + Q < m, & if \quad z = 0 \\ P + Q = m, & if \quad z = 1 \\ P + Q > m, & if \quad z > 1 \end{cases}$$

(16)

Since the traditional addition of 'P' and 'Q' needs to be

subtracted by mod 'm', the covering on bit short one can be utilized to get the desired result.

$$SUM1 = \underbrace{0...0}_{q \text{ zeros}} \underbrace{0...0}_{p \text{ zeros}} \underbrace{1...1}_{z-1}$$

(17)

During the modular addition P+Q, the number of zeros is significant if the result is less than'm'. Like the previous example, the bitwise-OR operation between the flipped versions of 'Q' and 'P' is considered.

$$P = \underbrace{0...0}_{p_{\text{zeros-z}}} \underbrace{0...0}_{z} \underbrace{1...1}_{p_{\text{ones}}}$$

(18)

$$Q_{reverse} = \underbrace{1 \dots 1}_{q \text{ ones}} \underbrace{0 \dots 0}_{z} \underbrace{0 \dots 0}_{q_{\text{zeros-z}}}$$

(19)

$$P \lor Q_{reverse} = \underbrace{1...1}_{Q_{ones}} \underbrace{0...0}_{z} \underbrace{1...1}_{p_{ones}}$$

(20)

The output contains (Pones + Qones) bits with z-zeros if P+Q < m.

$$SUM0 = \underbrace{0...0}_{z} \underbrace{1...1}_{q \text{ ones}} \underbrace{1...1}_{p \text{ ones}} \underbrace{1...1}_{q \text{ ones}}$$

(21)

The mod adder for the mod '7' based on TCR is shown in Fig. 2.<sup>[22]</sup> Multiplexers (MUXs) and logic gates were the only components used in the construction of the adder. SUM1 stores the result of this adder when total  $\geq$  mod value, while SUM0 stores the result when P+Q < mod value. Depending on the logic level on 'Set', MUX can produce either SUM0 or SUM1 as the adder's output. The 'Set' was the NOR gate's output, which received its inputs from AND gates' outputs, which contained the inputs 'P' and 'Q', bit reversed.

Fig. 2: Mod-7 Adder Based on TCR<sup>[22]</sup>

Another mod adder based on TCR was proposed in [27].In this how the adder performed the addition process was

Journal of VLSI circuits and systems, ISSN 2582-1458

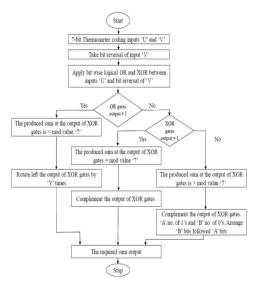

presented. Here, based on the Thermometer Coding idea, another mod adder that is more power-efficient than current adders is proposed. In this mod adder, input integers that participate in addition can be indicated in TC using m-bits. The following can be used to calculate the modular addition of two numbers using the flow chart shown in Fig. 3.

Once both inputs have been represented using Thermometer Coding (TC), the first number is regarded as 'U' and the second as 'V'. Before applying the input, the bit inverted value for 'V' must be determined to conduct logical OR and bitwise modulo-2 addition (XOR) simultaneously. The following step process finds overlapping zeros, denoted by 'p'.

The logic ' $p \ge 1$ ' can be used to determine the sum (U + V < m). Then, rotate the output of the XOR gates to the left by 'V' times. As illustrated in the equation below, the outcome appears to be a sequence of overlapping zeros (p) followed by a total of 1s are present in both the input integers 'U' and 'V'.

$$U + Vreverse = \underbrace{0...0}_{p_{\square}} \underbrace{1...1}_{uones} \underbrace{1...1}_{v_{ones}}$$

(22)

If the input integers do not have any overlapping zeros (p=0). This suggests that the sum is greater than the modulus'm' when the output of any OR gate is non-zero. To be more precise, the output of all XOR gates is logic '1' rather than the 'sum=m'. The result is obtained by inverting the XOR gates' outputs. Assume for the moment the results are xn xn-1...x2 x1.

$$U + Vreverse = xn^{1}xn \cdot 1^{1}....x2^{1}x1^{1}$$

(23)

Fig. 3: TCR-based Mod-7 Adder [27]

When zeros that intersect equal zero, that is a different case. This means that the result is made sum > modulusvalue 'm' if all OR gates give outputs that are not zero and all XOR gates give outputs that are not one. The outcome is added to the outputs of all XOR gates and sets up the 'A' number of 0's and 'B' number of 1's. This time, a certain number (B) of XOR gates makes zero, while the leftover number (A) of gates makes one.

$$U + Vreverse = \underbrace{0...0}_{B_{zeros}} \underbrace{1...1}_{A_{ones}}$$

(24)

### **Proposed Model**

One can review a new proposed TCR-based mod adder in this part. The suggested TCR-based mod adder resembles the TCR-based mod adder reported in [27]. In this proposed mod adder, the input numbers are represented with only 'm-1' bits, but in the case of [27], the inputs are represented with the 'm' number of bits. Because it uses a smaller number of bits, the proposed TCR-based mod produces better results than the mod adders mentioned in the previous section.

During the addition process, it is necessary to reverse the bits of the input 'V' before performing logical OR and XOR operations with the input 'U'. The logical OR operation is employed to validate the presence of overlapping zeros. If overlapping zeros exist, the resulting value is < 'm'. Otherwise, the resulting value is  $\geq$  'm'. In this scenario, the outcome can be achieved by left-rotating the output of the XOR gates by 'V' times. For a good understanding of the scenario, the following example is useful.

Example: Input Numbers U = 3 and V = 2 then the result of U + V.

Input U = 3 = 000111; Input V = 2 = 000011 The flipped version of V = 110000

-----

Logical OR b/w U and Flipped version of V = 110111Logical XOR b/w U and Flipped version of V = 110111Rotate left XOR gates output by 'V' times = 011111 = 5

Another scenario in this addition process was, no overlapping zeros between the 'U' and bit reversal of 'V', at the same time the out of the XOR gates is one, for this scenario the result is straightway the outcome of the XOR gates which is (m-1).

Example: Input Numbers U = 4 and V = 2 then the result of U + V.

Input U = 4 = 001111; Input V = 2 = 000011

The flipped version of V = 110000

Logical OR b/w U and Flipped version of V = 111111 Logical XOR b/w U and Flipped version of V = 111111 The XOR gates output is the result = 111111 = 6

-----

One more scenario in this addition process was, no overlapping zeros between 'U' and bit reversal of 'V', at the same time only one XOR gate output is equal to zero, which indicates the generated result = 'm'. To get the outcome, complement the XOR gates' output, which produces logic '1' at their output.

Example: Input Numbers U = 5 and V = 2 then the result of U + V.

Input U = 5 = 011111; Input V = 2 = 000011 The flipped version of V = 110000

Logical OR b/w U and Flipped version of V = 111111 Logical XOR b/w U and Flipped version of V = 101111 Complement the XOR gates output, whose output is '1', to get the result = 000000 = 0

The final scenario in this addition process was there were no intersecting zeros between 'U' and bit reversal of 'V'. In the addition process complement the XOR gates output at the time some 'M' no. of XOR gates generated logic '0', a 'N' no. of XOR gates generated logic '1'. For this case, get the result (M+1) number of zeros followed by (N-1) number of ones.

Example: Input Numbers U = 6 and V = 2 then the result of U + V.

Input U = 6 = 111111; Input V = 2 = 000011 The flipped version of V = 110000

Logical OR b/w U and Flipped version of V = 111111 Logical XOR b/w U and Flipped version of V = 001111 Complement the XOR gates output = 110000 The result of the addition = 000001 = 1

Fig. 4 displays the flow chart of the suggested TCR-based mod adder.

The pseudo system verilog code of the suggested TCRbased mod adder is as follows.

```

module model_1#(parameter N)(A,B,out);

input [N-2:0] A;

input [N-2:0] B;

output reg [N-2:0] out;

```

| - | - | - | - | - | - | - | - | - | - |   |

|---|---|---|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - | - | - | - |

| - | - | - | - | _ | - | - | - | - | - | - |

| _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ |

always@(\*) begin if(count overlap zeros > {(N/2){1'b0}}) begin ---------function [N-1:0] convert input; input [N-1:0] in\_1; reg [N-1:0] out\_1; integer l,m; begin ---------endfunction function [(N/2)-1:0] count\_zeros; input [N-1:0] in; \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ ----end endfunction function [N-1:0] reverse\_in; input [N-1:0] in1; reg [N-1:0] temp; - - - - - - - - - - -\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ endfunction endmodule All OR g Sum produced at the itput of XOR gates < m-1

# Fig. 4: Proposed TCR-based Mod Adder

### **EXPERIMENTAL RESULTS**

m produced

The current mod adder and recommended one based on the TC model are simulated using the Cadence NC launch simulation analysis environment. The delay, total power consumption, area, power delay product (PDP), and area delay product (ADP) comparison of the TCR-based

Journal of VLSI circuits and systems, ISSN 2582-1458

modulo adder, the proposed 90nm TCR-based mod adder design in the Encounter tool, and the existing TCR-based mod adder are shown in Tables 2, 3, 4,5, and 6. According to the Tables, the suggested design outperforms current solutions with acceptable areas and delays in terms of power consumption and power delay product.

The proposed modulo adder consumes less power compared to the existing system. One of the main reason for this is the number bits are used for the representation of the input numbers in thermometer coding. The number of bits used in the proposed modulo adder 'm' adder is  $(m^{-1})$ -bits. The operation of the proposed adder is simple.

#### Table 2: Comparison of Delay (ns)

| Mod<br>Value | Suggested Mod Adder<br>[27] |      | Mod Adder<br>[22] | Mod Adder<br>[21] |

|--------------|-----------------------------|------|-------------------|-------------------|

| 7            | 1.56 1.93                   |      | 1.06              | 2.09              |

| 8            | 1.64                        | 1.98 | 1.21              | 2.30              |

| 9            | 2.35                        | 2.88 | 1.44              | 3.51              |

| 11           | 2.46                        | 2.98 | 1.76              | 3.86              |

| 13           | 3.98                        | 4.48 | 2.06              | 5.31              |

Table 3: Comparison of Total Power (µW)

| Mod<br>Value | Suggested | Suggested Mod Adder<br>[27] |       | Mod Adder<br>[21] |

|--------------|-----------|-----------------------------|-------|-------------------|

| 7            | 3.16      | 3.88                        | 6.23  | 16.62             |

| 8            | 2.10      | 2.35                        | 7.43  | 11.76             |

| 9            | 2.18      | 2.69                        | 8.90  | 16.69             |

| 11           | 2.75      | 3.08                        | 13.32 | 21.78             |

| 13           | 4.98      | 6.97                        | 23.88 | 24.74             |

Table 4: Comparison of Area in (µm<sup>2</sup>)

|              |                          | •      |                   | ,                 |  |

|--------------|--------------------------|--------|-------------------|-------------------|--|

| Mod<br>Value | Suggested Mod Adder [27] |        | Mod Adder<br>[22] | Mod Adder<br>[21] |  |

| 7            | 301.32                   | 375.42 | 255.08            | 265.26            |  |

| 8            | 395.65                   | 448.84 | 326.22            | 348.25            |  |

| 9            | 410.36                   | 498.04 | 406.46            | 425.21            |  |

| 11           | 581.23                   | 600.97 | 602.49            | 623.54            |  |

| 13           | 687.43                   | 763.71 | 829.56            | 840.96            |  |

Table 5: Comparison of PDP in ( $\mu$ W \* ns)

| Mod<br>Value | Suggested Mod Adder<br>[27] |               | Mod Adder<br>[22] | Mod Adder<br>[21] |  |  |

|--------------|-----------------------------|---------------|-------------------|-------------------|--|--|

| 7            | 4.93                        | 4.93 7.49 6.6 |                   | 34.74             |  |  |

| 8            | 3.44                        | 4.65          | 8.99              | 27.05             |  |  |

| 9            | 5.12                        | 7.75          | 12.82             | 58.58             |  |  |

| 11           | 6.76                        | 9.18          | 23.44             | 84.07             |  |  |

| 13           | 19.82                       | 31.23         | 49.19             | 131.37            |  |  |

| Mod<br>Value | Suggested Mod Adder<br>[27] |         | Mod Adder<br>[22] | Mod Adder<br>[21] |  |

|--------------|-----------------------------|---------|-------------------|-------------------|--|

| 7            | 470.06                      | 724.56  | 270.38            | 554.39            |  |

| 8            | 648.87                      | 888.70  | 394.73            | 800.98            |  |

| 9            | 964.35                      | 1434.35 | 585.30            | 1492.49           |  |

| 11           | 1429.83                     | 1790.89 | 1060.38           | 2406.86           |  |

| 13           | 2735.97                     | 3421.42 | 1708.89           | 4465.50           |  |

Table 6: Comparison of ADP in (µm<sup>2</sup> \* ns)

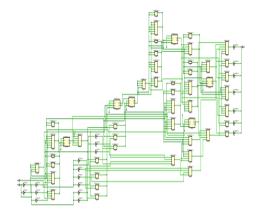

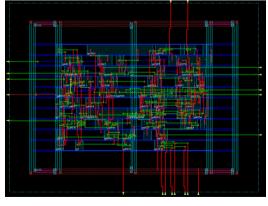

The RTL Schematic of the proposed adder is shown in below Fig. 5

Fig. 5: RTL Schematic of the Proposed Mod - 7 Adder The simulation results of the proposed TCR-based mod adder (mod value = 7) are shown in Fig. 6 and its layout is shown in Fig. 7.

| Name                      | Value  | 0 ns   |        | 10 ns  |        | 20 ns  |        | 30 ns  |        | 40 ns  | Lini   |

|---------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| > 💔 A[5:0]                | 06     | XX     | 03     | 02     | 04     | 0      | 6      | 03     | 02     | 05     | 06     |

| > 💔 B[5:0]                | 01     | xx     | 03     | 01     | 05     | 00     | 01     | 03     | 02     | 04     | 01     |

| ✓ <sup>1</sup> Ø OUT[5:0] | 000000 | 000000 | 111111 | 000111 | 000011 | 111111 | 000000 | 111111 | 001111 | 000011 | 000000 |

| 6 [5]                     | 0      |        |        |        |        |        |        |        |        |        |        |

| <b>a</b> [4]              | 0      |        |        |        |        |        |        |        |        |        |        |

| 16 [3]                    | 0      |        |        |        |        |        |        |        |        |        |        |

| 16 [2]                    | 0      |        |        |        |        |        |        |        |        |        |        |

| Ìø [1]                    | 0      |        |        |        |        |        |        |        |        |        |        |

| 16 [0]                    | 0      |        |        |        |        |        |        |        |        |        |        |

Fig. 6: Suggested Mod Adder Simulation Result

Fig. 7: Layout of the Proposed Mod Adder

### **CONCLUSION**

The proposed TCR-based mod adder in this paper gives good results in contrast to the existing similar mod adders based on TCR in terms of Delay, Total Power Consumption, Area, Power Delay Product (PDP), and Area Delay Product (ADP). By considering all these results of the suggested mod adder based on TCR it was suitable for applications like Embedded Systems, Digital Signal Processing, Digital Image Processing, Cryptography, communications, etc., In these applications power consumption, area, and delay are crucial.

## REFERENCES

- [1] Chen Y.H, Krishna T, Emer J. S, Sze V, Eyeriss. An energyefficient reconfigurable accelerator for deep convolution neural networks.In:IEEE International Solid State Circuits conference2016; 53, 1: 127-138.

- [2] Molahosseini A. S, Sousa L, Chang C. H (Eds.). Embedded Systems Design withSpecial Arithmetic and Number Systems, New York: Springer, 2017.

- [3] Alioto M (Ed). Enabling the Internet of Things: from Integrated Circuits to Integrated Systems, New York: Springer, 2017.

- [4] Chang C. H, Molahosseini A. S, Zarandi A. A. E, Tay T. F. Residue Number Systems: A new paradigm to data path organization for low power and high-performance digital signal processing applications. IEEE Circuits and Systems Magazine 2015; 15, 4: 26-44.

- [5] Rahim, Robbi. "Review of Modern Robotics: From Industrial Automation to Service Applications." Innovative Reviews in Engineering and Science 1.1 (2024): 34-37.

- [6] Ananda Mohan P. V. Residue Number Systems: Theory and Applications, New York: Springer, 2016.

- [7] Golomb S. W. Run-length encodings (Correspond). IEEE Transactions Information Theory 1996; 12, 3: 399-401.

- [8] Kumar, TM Sathish. "Low-Power Communication Protocols for IoT-Driven Wireless Sensor Networks." Journal of Wireless Sensor Networks and IoT 1.1 (2024): 24-27.

- [9] Abdullah, Dahlan. "Leveraging FPGA-Based Design for High-Performance Embedded Computing." SCCTS Journal of Embedded Systems Design and Applications 1.1 (2024): 29-32.

- [10] Vun C. H, Premkumar A. B. Thermometer code based modular arithmetic, In Spring Congress. Eng. Technology, May 2012, 534-38.

- [11] Vun C. H, Premkumar A. B. RNS encoding based folding ADC, In IEEE Int. Symp. Circuits, May 2012, 814-17.

- [12] K Vijaya Vardhan, M. Sarada, K. M. Santhoshini, A. Srinivasulu. A Critical Look at Modular Adders using Residue Number Systems, Solid State Electronic Letters 2019; 1, 2: 84-91.

- [13] Premkumar B, Omondi A. Residue Number Systems: Theory and Implementation, New York: (vol 2) World Scientific, 2007.

- [14] Patel R, Benaissa M, Boussakta S. Fast Modulo 2n (2n-2 + 1) addition: a new class of adder for RNS, IEEE Transactions on Circuits and Systems I 2007; 56,6: 1279-92.

- [15] Jaberipur G, Parhami B, Nejati S. On building general modular adders from standard binary arithmetic components, In 45thAsilomar Conf. Signals Systems and Computers, 2011, 6-9.

- [16] Ma S, Hu J, Wang C. H. A novel modular adder for 2n 2k

1 residue number system, IEEE Transactions on Circuits and Systems 2013; 60, 11: 2962-72.

- [17] K. VijayaVardhan, G Sailakshmi, M. Sarada, A. Srinivasulu. Analysis and Design of High-SpeedResidue to Binary Reverse Converter for the Moduli Set {2n + 1, 2n, 2n - 1}, In IEEE Recent Advances in Intelligent Computational Systems, December 2020,53-60.

- [18] Hiasat A. General Modular Adder designs for Residue Number System Applications, IET Circuits Devices Systems 2018; 12, 4: 424-31.

- [19] White S. A. Applications of distributed arithmetic to digital signal processing: A tutorial review, IEEEASSP Magazine 1989; 6, 3: 4-19.

- [20] J. K. Saini, A. Srinivasulu, B. P. Singh. A new low-power full-adder cell for low voltage using CNTFETs, In IEEE

International Conference on Electronics, Computers, and Artificial Intelligence 2017, 6-10.

- [21] T. Nagateja, T. Venkata Rao, A. Srinivasulu. Low Voltage, High-Speed FinFET based 1-bit BBL-PT Full Adders, In IEEE International Conference on Communication and Signal Processing 2015, 1247-51.

- [22] Jafarzadehpour F, A. S. Molahosseini, A. A. E. Zarandi, L. Sousa. Efficient Modular Adder Designs Based on Thermometer and One-Hot Coding, IEEE Transactions on Very Large Scale Integration Systems 2019; 27, 9: 2142-55.

- [23] P. V. Lakshmi, M. Sarada, A. Srinivasulu, D. Pal. Three Novel Single-Stage Full-Swing 3-input XOR, International Journal of Electronics 2018; 105, 8: 1416-32.

- [24] M. Sarada, A. Srinivasulu, D. Pal. Novel Low-Supply, Differential XOR/XNOR with Rail-to-Rail Swing for Hamming Code Generation, International Journal of Electronics Letters 2018; 6, 3: 272-87.

- [25] M. Sarada, A. Srinivasulu. Two DCVSL XOR/XNOR Circuits Operated at Sub-Threshold Voltages Using MOSFETS and FinFETs, Journal of Advanced Research in Dynamical and Control Systems 2017; 9, 2: 123-134.

- [26] Green, K., and R. Vrba. "Research on Nano Antennas for Telecommunication and Optical Sensing." National Journal of Antennas and Propagation 6.2 (2024): 1-8.

- [27] K Vijaya Vardhan, and Sarada Musala, "Ultra-Low-Power Modulo Adder with Thermometer Coding for Uncertain RNS Applications", Journal of Uncertain Systems 2022, 15, 3, 12-20.