WWW.VLSIJOURNAL.COM

# Fundamental Data Seperator using Threshold Logic at Low-Supply Voltages

Q. Hugh<sup>1</sup>, Freddy Soria<sup>2</sup>, C.C. Kingdon<sup>3</sup>, Robert G. Luedke<sup>4</sup>

Robotics and Automation Laboratory Universidad Privada Boliviana Cochabamba, Bolivia

#### **KEYWORDS:**

CMOS; Delay; FinFET; HVT; LVT; Power..

#### ARTICLE HISTORY:

Received 22.07.2022 Accepted 10.08.2022 Published 20.09.2022

#### DOI:

https://doi.org/10.31838/jvcs/04.02.05

#### Abstract

In digital terminology, a device that compares two numbers which are represented in binary format and determines whether one of the two inputs are lesser than or equal to or greater than the other input is called a comparator. Comparators are generally used in Central Processing units (CPUs) and microcontrollers. In this project, a 2-bit magnitude comparator is designed with 18nm FinFET technology. FinFET technology is used to overcome the drawbacks associated with CMOS technology like channel length, power consumption, delay and area of transistors, etc. The proposing magnitude comparator is compared with the existing CMOS comparator in terms of power and delay. Schematic circuit diagrams of greater than, equal to and lesser than circuits have been simulated using the Cadence Virtuoso tool. Power and delay values are calculated and plotted for different values of supply voltage ranging from 0.1v-1.0v. LVT (Low Voltage) and HVT (High Voltage) analysis are performed separately. FinFET comparators can be used where a fast switching rate is required, to improve the efficiency of control devices and to make devices compact.

Author's e-mail: Hugh.q@upb.edu, soria.fred@upb.edu, kingdon.cc@upb.edu, robert.g.lu@upb.edu

How to cite this article: Hugh Q, Soria F, Kingdon CC, Luedke RG. Fundamental Data Seperator using Threshold Logic at Low-Supply Voltages. Journal of Complementary Research, Vol. 4, No. 2, 2022 (pp. 30-37).

## INTRODUCTION

Most of the arithmetic components in digital systems use comparator as a basic element or component. Not only in digital systems, comparators are also used in many hardware components for various applications due it its efficient performance, packed component, and cost factor, thus playing a major role in various components and circuits. These comparator components can be utilized individually when the main purpose is for comparing or these components can be integrated into various circuits where comparison is a small part of any application. Comparators are mainly used in governing and inspecting processes and these analyses are used according to the requirement.<sup>[1-7]</sup> They are widely used in limit setting equipment like the maximum or minimum temperature that something can withstand, in other words, the tolerance of a component. This means, the range can be established through comparator. Various control systems mainly use comparator as the basic element. Comparators are also used in quality assurance of products. Quantity measurements like weighing machines make use of comparators. It is also used in image processing and signal processing. The applications of comparator are many thus; they are used in daily life. They are also used in operating motors like Brushless Direct Current motors. Comparators are used for efficiency checking of components in less time. Analog to digital conversions digital communication receivers and dc-dc converters also use comparators.[8-12] Comparators are also used in different generators: zero-crossing detector, window generator, time marker generator and phase detector. Applications of comparator are many. The operation of comparator also deals with only three outputs viz. greater than, lesser than or equal. At no case, all the three outputs become true, in other words, if one output is true among the three outputs, the remaining two outputs must and should become false.[13]

Power and delay are the two major concerns when it comes to analyzing the performance of a comparator. Various methods have been proposed to enhance the performance statistics of comparators.

The existing models were fabricated using different logics of MOSFET technology .[14-17] These logics include CMOS with domino logic, coupler logic etc. Different logics are incorporated with the same technology MOSFET to decrease the power consumption, increase the speed of operation and reduce the area of transistors. In VLSI, reducing all the factors is not possible, that is, we can only reduce one parameter at a time. Based on the application or the requirement, the associated factors can be reduced. CNTFET is also an existing technology. It stands for Carbon Nano Tube Field Effect Transistor. It uses single carbon nanotube or an array of carbon nanotubes as the channel material instead of bulk silicon as used in MOSFET structure. This technology is more advantageous when compared to CMOS technology as they are reliable and can withstand high temperatures. There are few common drawbacks that are associated with the existing technologies. Channel length is more, thereby increasing the area of the chip. Due to increased area, the delay will also be more which considerably decreases the speed. The drive current is also less in the existing technologies.<sup>[18,19]</sup>

Due to the drawbacks of the existing technology, this project is aimed to overcome the drawbacks with the help of new technology known as FinFET. FinFET stands for Fin Field Effect Transistor. In other words, FinFET is a multi-gate transistor. 18nm is the channel length between source and drain. FinFET technology has many advantages when compared with the existing technologies. Many types of FinFET are available. Drive current is high. Channel length is very less. Delay will be less, thereby increasing the speed of operation. Suppressed short channel effect is present. As the channel length is very less, a greater number of FinFETs can be embedded on a given area. For Very Large-Scale Integrated Circuit designs (VLSI), we generally use Cadence Virtuoso tools for simulation and results. It is designed to help the users in creating and manufacturing robust designs to explore, analyze, and verify a design against design goals so that one can maintain design intent throughout the design cycle. SoC design engineers mainly use cadence products to move a design into packaged silicon or emulation hardware or for FPGA prototyping. In Cadence, we use FinFET libraries and associated transistors to implement analyze the design of comparator.[20-22]

This paper deals with the introduction of comparators and their uses. The existing technologies like MOSFET and CNTFET are compared. It also describes about the drawbacks of the existing technology which can be dealt with the new technology FinFET. The advantages of FinFET play a major role in the enhancement of VLSI. The detailed explanation about the structure of FinFET is explained. This literature survey forms a basis for the methodology to be implemented and for analyzing the results obtained through simulation. The block diagram and the functionality of comparator are explained through truth table. The 2-bit magnitude comparator using n-channel transistor logic is explained by considering different cases like greater than, lesser than and equal to as a part of methodology. The 2-bit magnitude comparator circuits are simulated to obtain transient response. Power and delay values are obtained for lesser than, greater than and equal to circuits. The behavior of power and delay are noted and plotted by varying the supply voltage from 0V to 1V for both LVT and HVT configured transistors in FinFET technology. In the end, the conclusions and future scope of this project is obtained through simulation results. It also explains about the drawbacks of FinFET which can be studied further. References and supporting materials to carry out the project are added at the end of the paper.

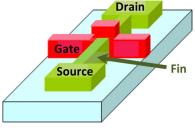

# FINFET CHARACTERISTICS AND MODELING

FinFET stands for Fin Field Effect Transistor. It is also called as multi-gate MOS transistors. In FinFET, the conducting channel is wrapped by silicon wafer which forms the substrate for the transistor. The channel length is determined by the thickness of the device. It is a nonplanar transistor. It generally consists of 2 gates. This double gate transistor is either based on silicon wafers or Sol (Silicon on Insulator). The base in which it gets fabricated determines the type of FinFET. To suppress or reduce the off-state leakage current and to allow good amount of current in drive state or ON state we use multi gates in FinFET. These multi gates also help to control the channel electrically. The performance issues on planar transistors can be overcome through FinFET technology. FinFET plays a major role in ULSI (Ultra Large Scale Integrated Circuits) products.<sup>[12, 13]</sup>

There are mainly two types of classification in FinFET: 1.Short Gate (SG) which are also called as 3T (three terminal) FinFETs. 2. Independent Gate (IG) which are also called as 4T (four terminal) FinFETs. The single gate transistor is classified in two types: 1. Bulk FinFET 2. Sol FinFET.

FinFET is the latest technology in VLSI domain. Because of its multi gate structure, it finds the following advantages: Drive current is more, Channel length is short implies that the design will be compact; Power

Fig. 1: Structure of FinFET

Journal of VLSI circuits and systems, , ISSN 2582-1458

consumption is less; Better performance; High speed. It is used in the processors due to its compactness as many FinFET transistors can be used within a specified area. Samsung Galaxy S6 uses FinFET technology in its processors. In future, the channel length will be decreased even more to FinFET 10nm. The given table represents the symbols, parameters and values associated with double gate FinFET.<sup>[15, 20]</sup>

# PROPOSED COMPARATOR BLOCK USING FINFET MODELS

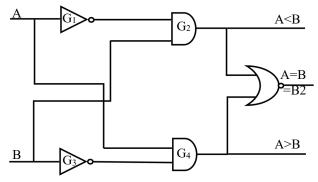

In the block diagram Fig. 2, A and B are 1-bit binary inputs and L (less than), E (equal to) and G (greater than) are three outputs based on the combination of inputs given.

$$G1 = A'$$

$G2 = B'$

$G3 = A'B$   $G4 = AB'$

$G5 = (A'B + AB')'$

The logic gate representation of magnitude comparator can be better represented and implemented using transistor level models. CMOS transistor which is a combination of both P-FINFET and N-FINFET is used to implement logic gates. We can also have only P-FINFET logic or only N-FINFET logic based on the requirement and input-output conditions. Transistor level implementation

Fig. 2: Block diagram of 1-bit magnitude comparator

Fig. 3: Lesser than functional circuit of 2-bit magnitude comparator

Journal of VLSI circuits and systems, , ISSN 2582-1458

is faster, suitable for larger designs and can handle longer simulation. In this project, FinFET technology is used for transistors. 2-bit magnitude comparator with inputs A0, A1, B0, B1 where A1, B1 represent MSB bit and A0, B0 represent LSB bit for the two numbers A and B are considered.

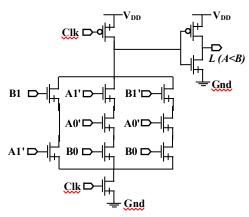

### Lesser than functional circuit

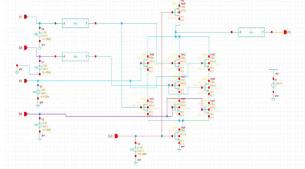

Lesser than functional implementation for 2-bit magnitude comparator as shown in Fig. 3 is represented in N-FINFET logic to represent A<B.

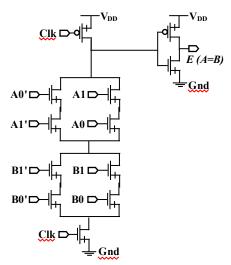

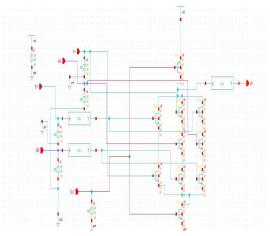

Equal to functional implementation for 2-bit magnitude comparator as shown in Fig. 4 is represented in N-FINFET logic to represent A=B.

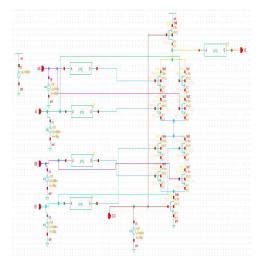

Greater than functional implementation for 2-bit magnitude comparator as shown in Fig. 5 is represented in N-FINFET logic to represent A=B.

Consider A and B are 2-bit binary inputs with A1, B1 as MSB bits and A0, B0 as LSB bits. The following expressions are:

L = A1'B1 + A0'B0B1 + A1'A0'B0

Fig. 4: Equal to functional circuit of 2-bit magnitude comparator

Fig. 5: Greater than functional circuit of 2-bit magnitude comparator

E = (A0B0 + A0'B0') (A1B1+A1'B1')G = A1B1' + A0B1'B0' + A1A0B0'

# SIMULATION RESULTS AND EXPERIMENTAL FINDINGS OF THE PROPOSED WORK

# Lesser than circuit design

Figure 6 represents schematic diagram of 2-bit lesser than circuit with LVT configured FinFET transistors. We can replace LVT transistors with HVT or NVT for comparison purposes. Inverter is a symbol created for another schematic diagram which is a pair n-LVT and p-LVT to inv

Fig. 6: Schematic diagram of 2-bit lesser than circuit

Fig. 8: Schematic diagram of 2-bit greater than circuit

Fig. 10: Transient response of 2-bit equal to circuit

# Equal than circuit design

Figure 7 represents schematic diagram of 2-bit equal to circuit with LVT configured FinFET transistors. We can replace LVT transistors with HVT or NVT for comparison purposes. Inverter is a symbol created for another schematic diagram which is a pair n-LVT and p-LVT in to invert the given input.

Fig. 7: Schematic diagram of 2-bit equal to circuit

Fig. 9: Transient response of 2-bit lesser than circuit

Fig. 11: Transient response of 2-bit greater than circuit

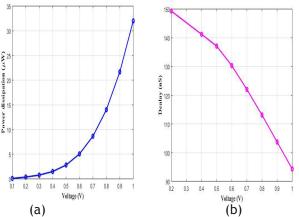

### Greater than circuit design

Figure 8 represents schematic diagram of 2-bit greater than circuit with LVT configured FinFET transistors. We can

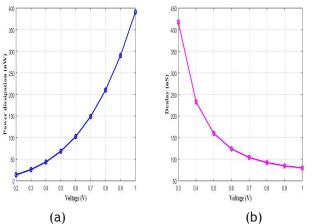

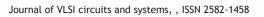

**Fig. 12: Equal to circuit at LVT** (a) Power vs Voltage plot (b) Delay vs Voltage Plot

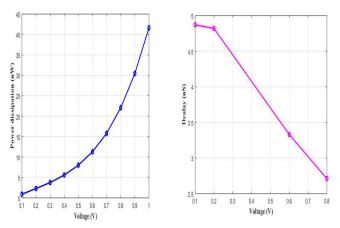

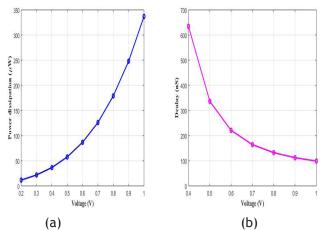

Fig. 14: Lesser than circuit at LVT (a) Power vs Voltage plot (b) Delay vs Voltage Plot

replace LVT transistors with HVT or NVT for comparison purposes. Inverter is a symbol created for another schematic diagram which is a pair n-LVT and p-LVT to invert the given input.

Fig. 13: Equal to circuit at HVT (a) Power vs Voltage plot (b) Delay vs Voltage Plot

Fig. 15: Lesser than circuit at HVT (a) Power vs Voltage plot (b) Delay vs Voltage Plot

34

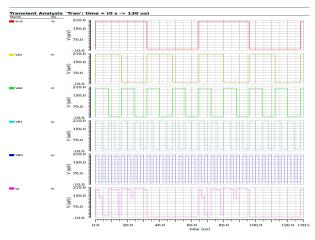

### Transient response plot of lesser than circuit

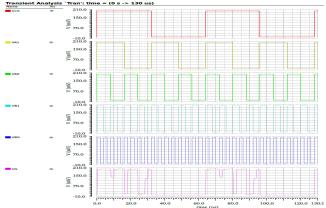

Figure 9, Figure 10 and Figure 11 are the simulation results obtained using spectre models for FinFET 18nm technology. The above transient response represents the overall functionality of comparator.

## **EXPERIMENTAL FINDINGS OF THE PROPOSED WORK**

## Power and Delay plots

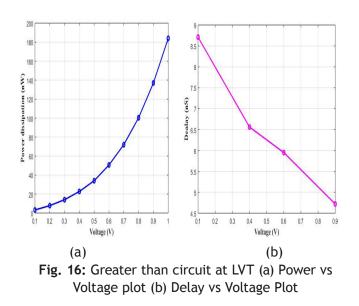

From the figures: Figure 12, Figure 13, Figure 14, Figure 15, Figure 16 and Figure 17: As the voltage increases, the power increases and as the voltage increases, the delay decreases for both LVT and HVT configurations. We can also infer that the delay for LVT is less when compared to HVT and the power consumption for LVT is more when compared to HVT.

# CONCLUSION

In this paper, a 2-bit magnitude comparator is designed with 18nm FinFET technology. FinFET technology is used to overcome the drawbacks like channel length, power consumption, delay, and area of transistors, etc. The proposing magnitude comparator is compared with the existing CMOS comparator in terms of power and delay. Schematic circuit diagrams of greater than, equal to and lesser than circuits have been simulated using the Cadence Virtuoso tool and spectre models. Power and delay values are calculated and plotted for different values of supply voltage. LVT (Low Voltage) and HVT (High Voltage) analysis are performed separately. The power values for LVT and HVT are increasing as the voltage increases. The power consumption of LVT is more when compared to HVT. The delay decreases as we increase the voltage levels. Delay for LVT is less when compared to the delay of HVT. The power-delay product is efficient when compared to the existing technologies like MOSFET. The distortions obtained at the transient response can be reduced by using suitable capacitors and other combination of logics associated with FinFET. Different types of FinFET can be used to obtain more efficient results. Normal threshold voltage can also be analyzed for comparison purposes.

## REFERENCES

- R.H. Krambeck, C.M. Lee, and H.S. Law, "High-speed compact circuits with CMOS," IEEE J. Solid-State Circuits, vol. 17, June 1982, pp. 614-619.

- [2] B. M. S. Rani, Vallabhuni Rajeev Ratna, V. Prasanna Srinivasan, S. Thenmalar, and R. Kanimozhi, "Disease prediction based retinal segmentation using bi-directional ConvLSTMU-Net," Journal of Ambient Intelligence and Humanized Computing, 2021, pp. 1-10. https://doi. org/10.1007/s12652-021-03017-y

- [3] Vallabhuni Vijay, C. V. Sai Kumar Reddy, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, M. Saritha, M. Lavan-

ya, S. China Venkateswarlu and M. Sreevani, "ECG Performance Validation Using Operational Transconductance Amplifier with Bias Current," International Journal of System Assurance Engineering and Management, vol. 12, iss. 6, 2021, pp. 1173-1179.

- [4] S. Swathi, S. Sushma, C. Devi Supraja, V. Bindusree, L. Babitha and Vallabhuni Vijay, "A Hierarchical Image Matting Model for Blood Vessel Segmentation in Retinal Images," International journal of system assurance engineering and management, vol. 13, iss. 3, 2022, pp. 1093-1101.

- [5] Bandi Mary Sowbhagya Rani, Vasumathi Devi Majety, Chandra Shaker Pittala, Vallabhuni Vijay, Kanumalli Satya Sandeep, Siripuri Kiran, "Road Identification Through Efficient Edge Segmentation Based on Morphological Operations," Traitement du Signal, vol. 38, no. 5, Oct. 2021, pp. 1503-1508.

- [6] Vallabhuni Vijay, and Avireni Srinivasulu, "A Novel Square Wave Generator Using Second Generation Differential Current Conveyor," Arabian Journal for Science and Engineering, vol. 42, iss. 12, 2017, pp. 4983-4990.

- [7] M. Lavanya, Malla Jyothsna Priya, Ponukumatla Janet, Kavuluri Pavan Kalyan, and Vijay Vallabhuni, "Advanced 18nm FinFET Node Based Energy Efficient and High-Speed Data Comparator using SR Latch," International Conference On Advances In Signal Processing And Communication Engineering (ICASPACE 2021), Hyderabad, India, July 29-31, 2021.

- [8] J. Sravana, K.S. Indrani, Sankeerth Mahurkar, M. Pranathi, D. Rakesh Reddy, and Vijay Vallabhuni, "Optimised VLSI Design of Squaring Multiplier using Yavadunam Sutra through Deficiency Bits Reduction," International Conference On Advances In Signal Processing And Communication Engineering (ICASPACE 2021), Hyderabad, India, July 29-31, 2021.

- [9] L. Babitha, U. Somanaidu, CH. Poojitha, K. Niharika, V. Mahesh, and Vallabhuni Vijay, "An Efficient Implementation of Programmable IIR Filter for FPGA," 1st International Conference on Innovations in Signal Processing and Embedded systems (ICISPES-2021), Hyderabad, India, October 22-23, 2021.

- [10] K. C. Koteswaramma, Ande Shreya, N. Harsha Vardhan, Kantem Tarun, S. China Venkateswarlu, and Vallabhuni Vijay, "ASIC Implementation of division circuit using reversible logic gates applicable in ALUs," 1st International Conference on Innovations in Signal Processing and Embedded systems (ICISPES-2021), Hyderabad, India, October 22-23, 2021.

- [11] Vallabhuni Vijay, J. Sravana, K.S. Indrani, G. Ajitha, A. Prashanth, K. Nagaraja, K.C. Koteswaramma, C. Radhika, M. Hima Bindu, N. Manjula, "A System for Controlling Positioning According To Movement Of Terminal in Wireless Communication based On AI Interface," The Patent Office Journal No. 50/2021, India. Application No. 202141055995 A.

- [12] Dr. L.V. Narasimha Prasad, Dr. Vijay Vallabhuni, Dr. S. China Venkateswarlu, Dr. V. Vhandra Jagan Mohan, Ms. P. Sruthilaya, Mr. K. Tarun Kumar, Mr. B. Raju, Mr. P. Ravinder, "Garbage Collector with Smart Segregation and Method of Segregation Thereof," The Patent Office Journal No. 04/2022, India. Application No. 202141062270 A.

- [13] Sravana, J., K. S. Indrani, M. Saranya, P. Sai Kiran, C. Reshma, and Vallabhuni Vijay, "Realisation of Performance

Optimised 32-Bit Vedic Multiplier," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 14-21.

- [14] V. Vijay, J. Prathiba, S. Niranjan Reddy, V. Raghavendra Rao, "Energy efficient CMOS Full-Adder Designed with TSMC 0.18µm Technology," International Conference on Technology and Management (ICTM-2011), Hyderabad, India, June 8-10, 2011, pp. 356-361.

- [15] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Optimal design of VLSI implemented Viterbi decoding," National conference on Recent Advances in Communications & Energy Systems, (RACES-2011), Vadlamudi, India, December 5, 2011, pp. 67-71.

- [16] Ratna, Vallabhuni Rajeev, and Ramya Mariserla. "Design and Implementation of Low Power 32-bit Comparator." (2021).

- [17] Vallabhuni Vijay, Kancharapu Chaitanya, T. Sai Jaideep, D. Radha Krishna Koushik, B. Sai Venumadhav, Rajeev Ratna Vallabhuni, "Design of Optimum Multiplexer In Quantum-Dot Cellular Automata," International Conference on Innovative Computing, Intelligent Communication and Smart Electrical systems (ICSES -2021), Chennai, India, September 24-25, 2021.

- [18] S. Sushma, S. Swathi, V. Bindusree, Sri Indrani Kotamraju, A. Ashish Kumar, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "QCA Based Universal Shift Register using 2 to 1 Mux and D flip-flop," IEEE 2021 International Conference on Advances in Computing, Communication and Control (ICAC3'21) 7th Edition (3rd and 4th December 2021), Mumbai, Maharashtra, India, December 03-04, 2021, pp. 1-6.

- [19] M. Sreevani, S. Lakshmanachari, B. Manvitha, Y.J.N. Pravalika, T.Praveen, V.Vijay, Rajeev Ratna Vallabhuni, "Design of Carry Select Adder Using Logic Optimization Technique," IEEE 2021 International Conference on Advances in Computing, Communication and Control (ICAC3'21) 7th Edition (3rd and 4th December 2021), Mumbai, Maharashtra, India, December 03-04, 2021, pp. 1-6.

- [20] M. Saritha, Chelle Radhika, M. Narendra Reddy, M. lavanya, A. Karthik, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "Pipelined Distributive Arithmetic-based FIR Filter Using Carry Save and Ripple Carry Adder," Second IEEE International Conference on Communication, Computing and Industry 4.0 (C2I4-2021), Bengaluru, Karnataka, India, December 16-17, 2021, pp. 1-6.

- [21] Vijay, Vallabhuni, M. Sreevani, E. Mani Rekha, K. Moses, Chandra S. Pittala, KA Sadulla Shaik, C. Koteshwaramma, R. Jashwanth Sai, and Rajeev R. Vallabhuni, "A Review On N-Bit Ripple-Carry Adder, Carry-Select Adder And Carry-Skip Adder," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 27-32.

- [22] Vijay, Vallabhuni, Chandra S. Pittala, A. Usha Rani, Sadulla Shaik, M. V. Saranya, B. Vinod Kumar, RES Praveen Kumar, and Rajeev R. Vallabhuni, "Implementation of Fundamental Modules Using Quantum Dot Cellular Automata," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 12-19.

- [23] Gollamandala Udaykiran Bhargava, Vasujadevi Midasala, and Vallabhuni Rajeev Ratna, "FPGA implementation of hybrid recursive reversable box filter-based fast adaptive bilateral filter for image denoising," Microprocessors and Microsystems, vol. 90, 2022, 104520.

- [24] Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, Vallabhuni Vijay, Usha Rani Anam, Kancharapu Chaitanya, "Numerical analysis of various plasmonic MIM/MDM slot waveguide structures," International Journal of System Assurance Engineering and Management, 2022.

- [25] Chandra Shaker Pittala, Vallabhuni Vijay, B. Naresh Kumar Reddy, "1-Bit FinFET Carry Cells for Low Voltage High-Speed Digital Signal Processing Applications," Silicon, 2022. https://doi.org/10.1007/s12633-022-02016-8.

- [26] S. Swathi, S. Sushma, V. Bindusree, L Babitha, Sukesh Goud. K, S. Chinavenkateswarlu, V. Vijay, Rajeev Ratna Vallabhuni, "Implementation of An Energy-Efficient Binary Square Rooter Using Reversible Logic By Applying The Non-Restoring Algorithm," Second IEEE International Conference on Communication, Computing and Industry 4.0 (C2I4-2021), Bengaluru, Karnataka, India, December 16-17, 2021, pp. 1-6.

- [27] Kiran, K. Uday, Gowtham Mamidisetti, Chandra shaker Pittala, V. Vijay, and Rajeev Ratna Vallabhuni, "A PCCN-Based Centered Deep Learning Process for Segmentation of Spine and Heart: Image Deep Learning," In Handbook of Research on Technologies and Systems for E-Collaboration During Global Crises, pp. 15-26. IGI Global, 2022.

- [28] Vallabhuni Vijay, V.R. Seshagiri Rao, Kancharapu Chaitanya, S. China Venkateshwarlu, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, "High-Performance IIR Filter Implementation Using FPGA," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [29] Jujavarapu Sravana, S.K. Hima Bindhu, K. Sharvani, P. Sai Preethi, Saptarshi Sanyal, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "Implementation of Spurious Power Suppression based Radix-4 Booth Multiplier using Parallel Prefix Adders," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-6.

- [30] Chandra Shaker Pittala, Vallabhuni Vijay, A. Usha Rani, R. Kameshwari, A. Manjula, D.Haritha, Rajeev Ratna Vallabhuni, "Design Structures Using Cell Interaction Based XOR in Quantum Dot Cellular Automata," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [31] S. China Venkateshwarlu, Mohammad khadir, V. Vijay, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, "Optimized Design of Power Efficient FIR Filter Using Modified Booth Multiplier," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [32] G. Naveen, V.R Seshagiri Rao, Nirmala. N, Pavan kalyan. L, Vallabhuni Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Design of High-Performance Full Adder Using 20nm CNTFET Technology," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [33] Vallabhuni Vijay, Pittala Chandra shekar, Shaik Sadulla, Putta Manoja, Rallabhandy Abhinaya, Merugu rachana, and Nakka nikhil, "Design and performance evaluation of energy efficient 8-bit ALU at ultra low supply voltages us-

ing FinFET with 20nm Technology," VLSI Architecture for Signal, Speech, and Image Processing, edited by Durgesh Nandan, Basant Kumar Mohanty, Sanjeev Kumar, Rajeev Kumar Arya, CRC press, 2021.

- [34] Mohammad khadir, S. Shakthi, S. Lakshmanachari, Vallabhuni Vijay, S. China Venkateswarlu, P. Saritha, Rajeev Ratna Vallabhuni, "QCA Based Optimized Arithmetic Models," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [35] P. Ashok Babu, P. Sridhar, and Rajeev Ratna Vallabhuni, "Fake Currency Recognition System Using Edge Detection," 2022 Interdisciplinary Research in Technology and Management (IRTM), Kolkata, India, February 24-26, 2022, pp. 1-5.

- [36] Koteshwaramma, K. C., Vallabhuni Vijay, V. Bindusree, Sri Indrani Kotamraju, Yasala Spandhana, B. Vasu D. Reddy, Ashala S. Charan, Chandra S. Pittala, and Rajeev R. Vallabhuni, "ASIC Implementation of An Effective Reversible

R2B Fft for 5G Technology Using Reversible Logic," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 5-13.

- [37] Vijay, Vallabhuni, Kancharapu Chaitanya, Chandra Shaker Pittala, S. Susri Susmitha, J. Tanusha, S. China Venkateshwarlu, and Rajeev Ratna Vallabhuni, "Physically Unclonable Functions Using Two-Level Finite State Machine," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 33-41.

- [38] M. Saritha, M. Lavanya, G. Ajitha, Mulinti Narendra Reddy, P. Annapurna, M. Sreevani, S. Swathi, S. Sushma, Vallabhuni Vijay, "A VLSI design of clock gated technique based ADC lock-in amplifier," International Journal of System Assurance Engineering and Management, 2022, pp. 1-8. https://doi.org/10.1007/s13198-022-01747-6

- [39] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Low power based optimal design for FPGA implemented VMFU with equipped SPST technique," National Conference on Emerging Trends in Engineering Application (NCE-TEA-2011), India, June 18, 2011, pp. 224-227.