WWW.VLSIJOURNAL.COM

# ADC: Novel Methodology for Code Converter Application for Data Processing

Haitham M. Snousi<sup>1</sup>, Fateh A. Aleej<sup>2</sup>, M. F. Bara<sup>3</sup>, Ahmed Alkilany<sup>4</sup>

<sup>1-4</sup>Department of Computer Science, Faculty of Science, Sebha University Libya

#### **KEYWORDS:**

Binary code; Encoder; Flash ADC; Gray Code; Multiplexer; XOR gate.

#### ARTICLE HISTORY:

Received 14.07.2022 Accepted 22.08.2022 Published 20.09.2022

DOI: https://doi.org/10.31838/jvcs/04.02.07

#### **Abstract**

An innovative "Multiplexer based Thermometer to Binary code encoder" is presented in this paper. This paper shows a relative decrease in the total count of multiplexers used which eventually reduces the no of transistors used when compared to traditional Architectures. The requirement for further more inverters is also eliminated in the proposed model. The input thermometer code is at first is converted to the respective gray code with the help of 2:1 multiplexer. Thereafter, using two-input XOR gates the conversion process of gray code to respective binary codes takes place. Outcomes of simulation reveal that there is an approximately 80% decrease in the power consumption which is a great reduction actually when differentiated with previously known and current encoder architectures with the delay being reduced from 0.472ps to 0.366 ps. This throws a light on modern power-saving encoder architectures and has a greater significance in the future. The proposed encoder gives a better application for future generation advanced ADC & related circuits.

Author's e-mail: ms.haitham@gmail.com, aleej.fa@gmail.com, bara.mf@gmail.com, alkilany.ah@gmail.com

How to cite this article: Snousi HM, Aleej FA, Bara MF, Alkilany A. ADC: Novel Methodology for Code Converter Application for Data Processing. Journal of Complementary Research, Vol. 4, No. 2, 2022 (pp. 46-56).

## **INTRODUCTION**

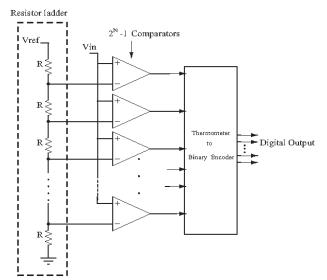

One of the key operating unit in digital signal processing and system on chip applications is 'Analog to digital convertors' (ADC). For immense rapidity & applications on low resolution, the flash Analog to digital convertor is relatively used amidst various ADC design models.<sup>[1-4]</sup> Figure 1 displays the design model of flash ADC.<sup>[5-7]</sup>

Using thermometer to binary encoder, the outputs of comparator are converted to binary code. The ADC displayed in the image below has '2N -1' comparators for the 'N-bit resolution', in which reference voltage (V-ref) is being compared with the given input (analog signal) to provide the output as 'one' or 'zero'.<sup>[8-21]</sup>

There is necessity to construct ADC with greater rapidity, there by consuming fewer power, considering the fact that delay and power are the most significant elements in Integrated Circuit design. The traditional encoder designs present in "flash ADC" consumes more power and has a large delay.<sup>[22-31]</sup>

Therefore, an advanced model encoder is being proposed in the paper that actually uses/absorbs

Journal of VLSI circuits and systems, , ISSN 2582-1458

less amount of power and has very less delay when differentiated with existing and traditional and current encoder designs.  $^{[8\cdot9]}$

46

## Significant Drawbacks in the Existed Methods

In the existed methods the power consumption is more. This makes the circuit to draw or consume a lot of power. The existed model does not permit high integration levels. Due to their higher threshold voltage, previously known methods cannot be operated at low voltages.<sup>[32-39]</sup>

This tells us that the previously known and current known methodologies had a significant drawback which creates the need to invent new methodologies to make the circuit more efficient. It is also known that the static leakage current is also more in existing and previously known methodologies. There is high off-state current in MOSFET which is a major disadvantage. Existing models does not allow MOS technology to stay on track with Moore's law.

### **Proposed Design**

The architecture or design model for the proposed design 4-bit encoder is displayed in the Figure 10 which is constructed based on 3-bit encoder design as shown in the fig 9. The basic blocks of the proposed model are "2:1 multiplexer" and "2-input XOR gate". After conversion process of thermometer code using "2:1 MUX" we get gray code as output as shown in Table 2 & the resultant binary code is acquired with the help of gray code from "2-input XOR gates" as displayed in the Figure 4.3. Here the input data one ('1') of a few of the multiplexers are linked or joined to ground node, to lessen the no of multiplexers & eliminate the requirement of extra inverters which when contrasted to the previously known models.

To achieve less power consumption, the "2:1 multiplexer" and "2-input XOR gates" are exercised using reliable methods of realizing through transmission logic gate [14]. Then the resulting binary code is acquired from gray code after successfully converting it with the help of XOR gates which is purposely done to increase the security and encrypting the information.

The implementation and methodologies used has a greater impact in the present generation advanced processors and enhanced security features when contrasted and differentiated with the existing or previously known models. The previously known models had a lot of drawbacks and disadvantages and hence we came up with a modern approach to implement new generation encoder designs which is actually more powerful and efficient than previously known models.

#### **Paper Organization**

Therefore, the main operation of 'Analog to digital convertors' is change or convert the given input (analog signal) to digital data. If suppose an input (analog) which is to be converted is sent to a machine (let it be a personal computer) then to process the analog information to the machine there must be an ADC which can carry out the task of converting. This task of converting or processing analog information and changing into Distortion-Less digital data is carried out by 'Analog to digital convertor'. So, from the above stated information we came to know that there is need for ADC.

## **FINFET CHARACTERISTICS AND MODELING**

### **FinFET description and Operation**

FinFET is called as "Fin Field Effect Transistor", a kind of "3D" transistor extensively used in modeling the advanced future generation processors. Generally, FinFET models make use of a sort of conducting channel which will rise more than the level/limit of the insulator, making a very skinny layer of 'Si' construct which resembles the shape of a fin, called as gate electrode. Multiple gates can be allowed to operate on a single transistor using fin shaped electrode. This process is actually an extension of Moore's law, there by letting semiconductor manufacturers to design memory blocks and CPUs that are smaller in size, enabling faster performance, and also consume less power.

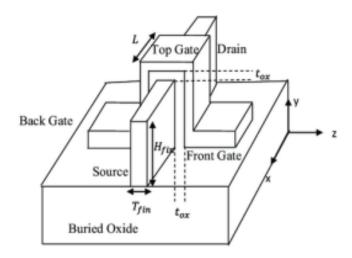

The main structure/element of the device which is actually formed by encasing conducting channel by a very light layer of Si "fin", which actually forms, is one of the key characteristics of FinFET. The basic layout of a FinFET and operation modes of a FinFET will not vary from traditional FET. The FinFET device Schematic is shown in the figure 2.

To manage the current flow, one source, one drain and also a gate is present. When compared with "planar MOSFET", the channel present between drain & source is designed as "3D" bar on upper part of the "Si" substrate which is known as fin. The gate electrode is encased all over the channel.

So, many gate electrodes on each side is formed leading to decrease in the discharge of charge and an intensified drift charge/current which helps overcoming some other short-channel effects. When the device is in the 'off' state

Fig. 2: FinFET Device Schematic

47

and when the channel is extended, there will be very small discharge of charge through the body. This will bring down threshold voltages and gives good performance and lower power consumption.

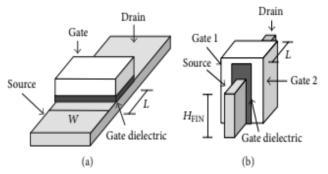

The figure 3 shows the comparison of construction between Planar MOSFET and FinFET

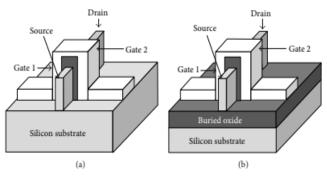

The figure 4 shows the comparison of construction between bulk and SOI FinFETs

## **Advantages of FinFET**

In FinFET technology, the utilization of power is less. This makes the circuit to draw or consume less power. The FinFET technology permit high integration levels. Due to their lower threshold voltage, it can be operated at low voltages.

This tells us that the FinFET technology has a great advantage than previously known and current known methodologies which make the circuit more efficient. It is also known that the static current leakage is less when differentiated to existing and previously known methodologies. There is low off-state current in FinFET which is a major advantage. FinFET technology allows MOS technology to stay on track with Moore's law.

## **Applications of FinFET**

As both gates can be conveniently controlled separately, it results in less power consumption. Threshold voltage of

Fig. 3: Comparison of construction between (a) planar MOSFET & (b) FinFET

Fig. 4: Comparison of construction between (a) bulk and (b) SOI FinFETs

Journal of VLSI circuits and systems, , ISSN 2582-1458

the device can be controlled by 2nd gate, which permits faster switching capabilities on one side and decreased current leakages when the circuit is unused. Finally, individual access to both gates can be used to develop a better simple logic gate. This would result in less power consumption, and also save area of the chip, leading to efficient & enhanced designs. In conclusion, we can understand that FinFET technology has more advantages than the previously known & currently used technology. This throws a light on designing future encoders using this technology which shows better performance.

## PROPOSED 4-BIT ENCODER BLOCK USING FINFET MODELS

## Wallace Tree Encoder

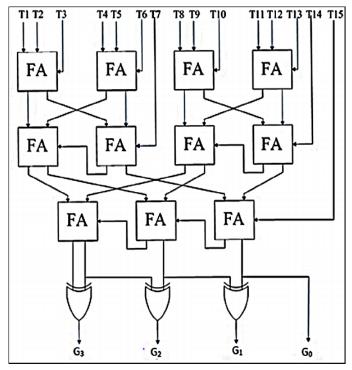

It generally checks and calculates the number of ones in the thermometer code (input) at the first level & provides the output as 2-bit binary code. After this initial stage, in an effort to get a required regular structure, two-bit data of the adjacent cells 2 by 2 are added. The same process of structuring follows up on for 3rd level resulting 4-bit gray code outputs as shown in Figure 5 and Table 1. Hence, it is also called as "Ones counter" [10]. The counter mechanism can be chosen on the basis of the speed of ADC. As the framework is designed using full adder, which has many transistors, which results in increased power consumption. So, the structure consumes large power and the delay also increases which is a major drawback.

Fig. 5: Wallace Tree Encoder

48

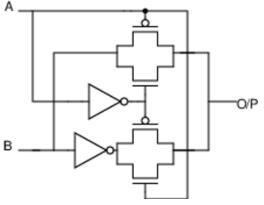

### *Realization of XOR gate with the help of Transmission gate*

The Figure 6 shows is multiplexer implemented using transmission gate.

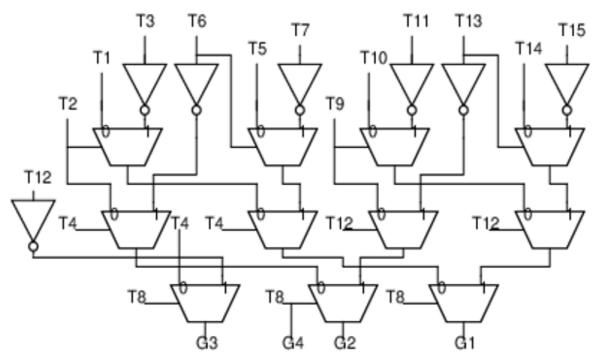

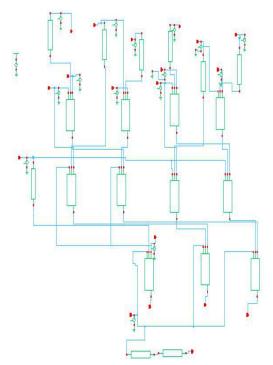

# Conventional Mux based Encoder description and operation

In this model 2:1 Multiplexer is used to attain less power consumption and less delay when differentiated with Wallace tree encoder. As it operates at greater speed and occupies small area of chip in comparison to above discussed architecture, this design model is generally used for designing flash ADCs. Figure 7 puts on view of the design of existing MUX based encoder.<sup>[11-12]</sup> The Self Re-configurable property<sup>[13]</sup> is a plus point for MUX based encoder in which

Fig. 6: Realization of XOR gate with the help of Transmission gate

similar encoder is used for several applications. This design has a drawback of large fan-out which has an increased view on the overall power consumption. The circuit shown below is existing MUX based encoder.

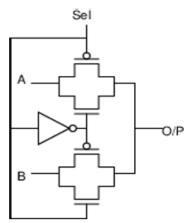

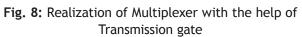

## *Realization of Multiplexer with the help of Transmission gate*

The Figure 8 shown below is multiplexer implemented using transmission gate logic.

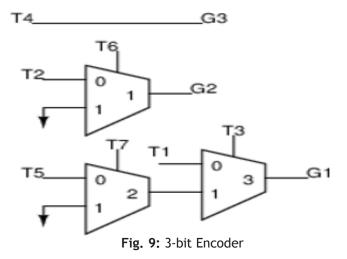

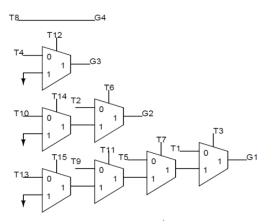

## Mux Encoder using Thermometer code description and operation

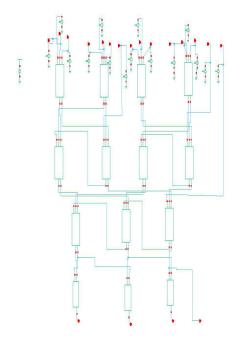

The architecture or design model for the proposed design 4-bit encoder is displayed in the Figure 10 which is constructed based on 3-bit encoder design as shown in the Figure 9. and the truth table for 3-bit encoder is displayed in the table 1.2. The basic blocks of the proposed model are "2:1 multiplexer" and "2-input XOR gate". After conversion process of thermometer code using "2:1 MUX" we get gray code as output as shown in Table 1.1& the resultant binary code is acquired with the help of gray code from "2-input XOR gates".

### 3-bit Encoder

3-bit encoder taken as reference for constructing 4-bit encoder

$$\begin{split} G_3 &= T_4 \\ G_2 &= T_2 \overline{T_6} \\ G_1 &= T_1 \overline{T_3} + T_3 \left( \overline{T_7} T_5 \right) \end{split}$$

Gray Output

|     |     |     |     |     |     | 1110 | ermon | ietei     | coue |    |    |    |    |    |    | Gro | ay Outp | Jul |

|-----|-----|-----|-----|-----|-----|------|-------|-----------|------|----|----|----|----|----|----|-----|---------|-----|

| T15 | T14 | T13 | T12 | T11 | T10 | Т9   | Т8    | <i>T7</i> | T6   | T5 | T4 | Т3 | T2 | T1 | G4 | G3  | G2      | G1  |

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0     | 0         | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0       | 0   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0     | 0         | 0    | 0  | 0  | 0  | 0  | 1  | 0  | 0   | 0       | 1   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0     | 0         | 0    | 0  | 0  | 0  | 1  | 1  | 0  | 0   | 1       | 1   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0     | 0         | 0    | 0  | 0  | 1  | 1  | 1  | 0  | 0   | 1       | 0   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0     | 0         | 0    | 0  | 1  | 1  | 1  | 1  | 0  | 1   | 1       | 0   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0     | 0         | 0    | 1  | 1  | 1  | 1  | 1  | 0  | 1   | 1       | 1   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0     | 0         | 1    | 1  | 1  | 1  | 1  | 1  | 0  | 1   | 0       | 1   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0     | 1         | 1    | 1  | 1  | 1  | 1  | 1  | 0  | 1   | 0       | 0   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 1     | 1         | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 0       | 0   |

| 0   | 0   | 0   | 0   | 0   | 0   | 1    | 1     | 1         | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 0       | 1   |

| 0   | 0   | 0   | 0   | 0   | 1   | 1    | 1     | 1         | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1       | 1   |

| 0   | 0   | 0   | 0   | 1   | 1   | 1    | 1     | 1         | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1       | 0   |

| 0   | 0   | 0   | 1   | 1   | 1   | 1    | 1     | 1         | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 0   | 1       | 0   |

| 0   | 0   | 1   | 1   | 1   | 1   | 1    | 1     | 1         | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 0   | 1       | 1   |

| 0   | 1   | 1   | 1   | 1   | 1   | 1    | 1     | 1         | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 0   | 0       | 1   |

| 1   | 1   | 1   | 1   | 1   | 1   | 1    | 1     | 1         | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 0   | 0       | 0   |

TABLE 1: TRUTH TABLE OF 4: BIT ENCODER (THERMOMETER TO GRAY) CODE CONVERSION

Thermometer Code

Fig. 7: Existing MUX Based Encoder

|    | Thermometer Code |    |           |    |           |           |    | Gray Output |    |  |  |

|----|------------------|----|-----------|----|-----------|-----------|----|-------------|----|--|--|

| Τ7 | Тб               | Τ5 | <i>T4</i> | Т3 | <i>T2</i> | <i>T1</i> | G3 | <i>G2</i>   | G1 |  |  |

| 0  | 0                | 0  | 0         | 0  | 0         | 0         | 0  | 0           | 0  |  |  |

| 0  | 0                | 0  | 0         | 0  | 0         | 1         | 0  | 0           | 1  |  |  |

| 0  | 0                | 0  | 0         | 0  | 1         | 1         | 0  | 1           | 1  |  |  |

| 0  | 0                | 0  | 0         | 1  | 1         | 1         | 0  | 1           | 0  |  |  |

| 0  | 0                | 0  | 1         | 1  | 1         | 1         | 1  | 1           | 0  |  |  |

| 0  | 0                | 1  | 1         | 1  | 1         | 1         | 1  | 1           | 1  |  |  |

| 0  | 1                | 1  | 1         | 1  | 1         | 1         | 1  | 0           | 1  |  |  |

| 1  | 1                | 1  | 1         | 1  | 1         | 1         | 1  | 0           | 0  |  |  |

### 4-Bit Encoder

Expressions of conversion is written using Figure 10 Circuit Diagram of 4-bit Encoder

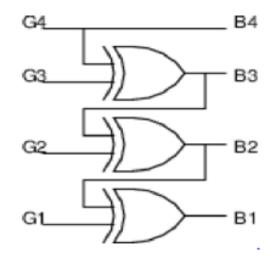

### **Gray to binary Conversion**

Generally Gray to binary conversion as displayed in table 3 is done just to increase the security and encryption mechanism. The conversion is shown in the below Figure 11.

Here the input data one ('1') of a few of the multiplexers are linked or joined to ground node, to lessen the no of multiplexers & eliminate the requirement of extra inverters which when contrasted to the previously known models. To achieve less power consumption, the "2:1 multiplexer" and "2-input XOR gates" are exercised using reliable methods of realizing through transmission logic gate.<sup>[14]</sup>

Fig. 10: 4-bit Encoder

Then the resulting binary code is acquired from gray code after successfully converting it with the help of XOR gates which is purposely done to increase the security and encrypting the information.

## SIMULATION RESULTS AND EXPERIMENTAL FINDINGS OF THE PROPOSED WORK

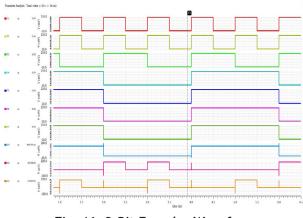

### Simulation Results of Wallace Tree Encoder

It generally checks and calculates the number of ones at the input at the first level and provides required output after processed through multiple levels. The below Figure 12 shown is Wallace tree encoder circuit. The waveform is displayed in figure 13.

Fig. 11: Gray to binary conversion

| TABLE 3: TRUTH TABLE FOR CONVERSION (INPUT GRAY CODE TO OUTPUT BINARY C | code) |

|-------------------------------------------------------------------------|-------|

|-------------------------------------------------------------------------|-------|

|    | Gr | ay Code Input |    |    | Binary Output |    |    |  |  |  |

|----|----|---------------|----|----|---------------|----|----|--|--|--|

| G3 | G2 | G1            | G0 | B3 | B2            | B1 | BO |  |  |  |

| 0  | 0  | 0             | 0  | 0  | 0             | 0  | 0  |  |  |  |

| 0  | 0  | 0             | 1  | 0  | 0             | 0  | 1  |  |  |  |

| 0  | 0  | 1             | 1  | 0  | 0             | 1  | 0  |  |  |  |

| 0  | 0  | 1             | 0  | 0  | 0             | 1  | 1  |  |  |  |

| 0  | 1  | 1             | 0  | 0  | 1             | 0  | 0  |  |  |  |

| 0  | 1  | 1             | 1  | 0  | 1             | 0  | 1  |  |  |  |

| 0  | 1  | 0             | 1  | 0  | 1             | 1  | 0  |  |  |  |

| 0  | 1  | 0             | 0  | 0  | 1             | 1  | 1  |  |  |  |

| 1  | 1  | 0             | 0  | 1  | 0             | 0  | 0  |  |  |  |

| 1  | 1  | 0             | 1  | 1  | 0             | 0  | 1  |  |  |  |

| 1  | 1  | 1             | 1  | 1  | 0             | 1  | 0  |  |  |  |

| 1  | 1  | 1             | 0  | 1  | 0             | 1  | 1  |  |  |  |

| 1  | 0  | 1             | 0  | 1  | 1             | 0  | 0  |  |  |  |

| 1  | 0  | 1             | 1  | 1  | 1             | 0  | 1  |  |  |  |

| 1  | 0  | 0             | 1  | 1  | 1             | 1  | 0  |  |  |  |

| 1  | 0  | 0             | 0  | 1  | 1             | 1  | 1  |  |  |  |

Fig. 12: Wallace Tree Encoder Circuit

|                                                                    | Virtueso (P) Visualization & Analysis XL | - 1                          |

|--------------------------------------------------------------------|------------------------------------------|------------------------------|

| Yew Graph Aris Iran: Warker Measurements Taols Window Brawser Help |                                          | câde                         |

| ■② (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)                         |                                          |                              |

| 🗄 🕕 Saberdans 1 🔒 🕸 😰 🖄 Das Fore                                   |                                          |                              |

| e wiltre scheradic X                                               |                                          |                              |

| 3cycae                                                             |                                          | FiiFeb714-4056202            |

|                                                                    |                                          |                              |

| • \$                                                               |                                          |                              |

| • E <sub>11</sub>                                                  |                                          |                              |

|                                                                    |                                          |                              |

| • § <sup>11</sup>                                                  |                                          |                              |

|                                                                    |                                          |                              |

| • § <sup>11</sup>                                                  |                                          |                              |

| • [\$ <sup>11</sup> ]                                              |                                          |                              |

| • §11 💵                                                            |                                          |                              |

| • [\$ <sup>11</sup> ]                                              |                                          |                              |

| • § <sup>11</sup>                                                  |                                          |                              |

|                                                                    |                                          |                              |

|                                                                    |                                          |                              |

| · • [\$"] ]                                                        |                                          |                              |

| • \$11                                                             |                                          |                              |

| δ • Σ <sup>11</sup> μ                                              |                                          |                              |

| • § <sup>11</sup>                                                  |                                          |                              |

|                                                                    |                                          |                              |

|                                                                    |                                          |                              |

|                                                                    |                                          |                              |

| * S                                                                |                                          |                              |

| • § ****                                                           |                                          |                              |

| • E 500                                                            |                                          |                              |

| 0 10 20 30 40 50 60                                                | 70 80 90 100 110 120 13                  | 0 140 150 160 170 160 190 2  |

| 94 LU 24 38 40 50 60                                               | cime (14)                                | 0 1900 ISU HU 170 IBU 1900 I |

|                                                                    | N2                                       |                              |

Fig. 15: Existing Mux Based Encoder Waveform

# Simulation Results of Conventional Mux based Encoder

In this model as shown in Figure 14 "2:1 Multiplexer" is used to attain less power consumption and less delay when differentiated with "Wallace tree encoder". The

ig. 14: Existing Mux Based Encoder Circuit

Fig. 16: 3-Bit Encoder Waveform

waveform of the circuit is shown in Figure 15. This design has a drawback of large fan-out which has an increased view on the overall power consumption.

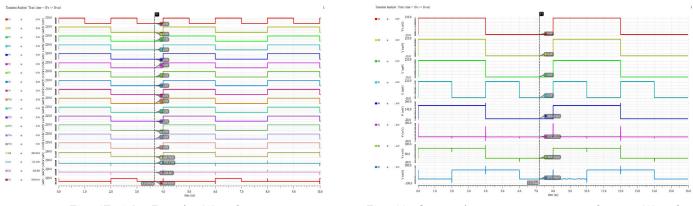

## Simulation Results of Mux Encoder using Thermometer code

## 4.3.1 3-Bit Encoder

The Figure 16 represents 3-bit encoder waveform

4-Bit Encoder (Thermometer coder)

The Figure 17 represents 4-bit encoder waveform

## Gray to binary Conversion

The Figure 18 represents Gray to binary code conversion waveform

Table 4 shows us the comparison for delay, PDP, EDP for all three encoder circuits.

Fig. 17: 4-Bit Encoder Waveform

0.698

Fig. 18: Gray to binary conversion verification Waveform

Power Power Delay Product Energy Delay Product Consumption Delay (PDP) (EDP) Structure (x10-24)J (x10-24)Js (mW)(ns) Wallace Tree Encoder 51.07 124 6.332 785.168 **Existing MUX Encoder** 2.45 0.472 0.0015 0.000708

0.366

TABLE 4: COMPARISON FOR DELAY, PDP, EDP FOR ALL THREE ENCODER CIRCUITS

## **Simulation results Analysis**

Proposed MUX Encoder

All the three encoder architectures discussed in the above chapters and design models are simulated using "Cadence software Simulator" at 18nm advanced technology. The Table 4 brings us a comparison between different encoder designs and performance analysis. Outcomes of simulation reveal that there is approximately 80% decrease in the power consumption which is a great reduction actually when differentiated with previously known and current encoder architectures with delay being reduced from 0.472ps to 0.366ps which tells us that the circuit performs faster than ever before. This throws a light on modern power saving encoder architectures and has a greater significance in future.

## CONCLUSION

In Conclusion, an innovative "Multiplexer based Thermometer to Binary code encoder" is presented in this paper. This paper shows a relative decrease in the total count of multiplexers used which eventually reduce the no of transistors used when compared to traditional Architectures. The requirement for further more inverters is also eliminated in the proposed model. The input thermometer code is at first is converted to the respective gray code with the help of 2:1 multiplexer. Thereafter, using two input XOR gates the conversion process of gray code to respective binary codes takes place. Outcomes of simulation reveal that there is approximately 80% decrease in the power consumption which is a great reduction actually when differentiated with previously known and current encoder architectures with delay being reduced from 0.472ps to 0.366 ps. This throws a light on modern power saving encoder architectures and has a greater significance in future. The proposed encoder gives a better application for future generation advanced ADC & related circuits.

0.000091

### REFERENCES

0.00025

- [1] Sunghyun Park, Yorgos Palaskas, and Michael P. Flynn, "A 4-GS/s 4-bit Flash ADC in 0.18nm CMOS," in IEEE Journal of Solid State Circuits, vol. 42, no. 9, Sep. 2007, pp. 1865-1872.

- [2] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Optimal design of VLSI implemented Viterbi decoding," National conference on Recent Advances in Communications & Energy Systems, (RACES-2011), Vadlamudi, India, December 5, 2011, pp. 67-71.

- [3] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Low power based optimal design for FPGA implemented VMFU with equipped SPST technique," National Conference on Emerging Trends in Engineering Application (NCETEA-2011), India, June 18, 2011, pp. 224-227.

- [4] Vallabhuni Vijay, and Avireni Srinivasulu, "A Novel Square Wave Generator Using Second Generation Differential Current Conveyor," Arabian Journal for Science and Engineering, vol. 42, iss. 12, 2017, pp. 4983-4990.

- [5] Ratna, Vallabhuni Rajeev, and Ramya Mariserla."Design and Implementation of Low Power 32-bit Comparator." (2021).

- [6] Vallabhuni Vijay, Kancharapu Chaitanya, T. Sai Jaideep, D. Radha Krishna Koushik, B. Sai Venumadhav, Rajeev Ratna Vallabhuni, "Design of Optimum Multiplexer In Quantum-Dot Cellular Automata," International Conference on Innovative Computing, Intelligent Communication and Smart Electrical systems (ICSES -2021), Chennai, India, September 24-25, 2021.

- [7] S. Sushma, S. Swathi, V. Bindusree, Sri Indrani Kotamraju, A. Ashish Kumar, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "QCA Based Universal Shift Register using 2 to 1 Mux and D flip-flop," IEEE 2021 International Conference on Advances in Computing, Communication and Control (ICAC3'21) 7th Edition (3rd and 4th December 2021), Mumbai, Maharashtra, India, December 03-04, 2021, pp. 1-6.

- [8] S. Swathi, S. Sushma, C. Devi Supraja, V. Bindusree, L. Babitha and Vallabhuni Vijay, "A Hierarchical Image Matting Model for Blood Vessel Segmentation in Retinal Images," International journal of system assurance engineering and management, vol. 13, iss. 3, 2022, pp. 1093-1101.

- [9] Bandi Mary Sowbhagya Rani, Vasumathi Devi Majety, Chandra Shaker Pittala, Vallabhuni Vijay, Kanumalli Satya Sandeep, Siripuri Kiran, "Road Identification Through Efficient Edge Segmentation Based on Morphological Operations," Traitement du Signal, vol. 38, no. 5, Oct. 2021, pp. 1503-1508.

- [10]M. Lavanya, Malla Jyothsna Priya, Ponukumatla Janet, Kavuluri Pavan Kalyan, and Vijay Vallabhuni, "Advanced 18nm FinFET Node Based Energy Efficient and High-Speed Data Comparator using SR Latch," International Conference On Advances In Signal Processing And Communication Engineering (ICASPACE 2021), Hyderabad, India, July 29-31, 2021.

- [11]J. Sravana, K.S. Indrani, Sankeerth Mahurkar, M. Pranathi, D. Rakesh Reddy, and Vijay Vallabhuni, "Optimised VLSI Design of Squaring Multiplier using Yavadunam Sutra through Deficiency Bits Reduction," International Conference On Advances In Signal Processing And Communication Engineering (ICASPACE 2021), Hyderabad, India, July 29-31, 2021.

- [12]L. Babitha, U. Somanaidu, CH. Poojitha, K. Niharika,

V. Mahesh, and Vallabhuni Vijay, "An Efficient Implementation of Programmable IIR Filter for FPGA," 1st International Conference on Innovations in Signal Processing and Embedded systems (ICISPES-2021), Hyderabad, India, October 22-23, 2021.

- [13]M. Sreevani, S. Lakshmanachari, B. Manvitha, Y.J.N. Pravalika, T.Praveen,V.Vijay, Rajeev

Ratna Vallabhuni, "Design of Carry Select Adder Using Logic Optimization Technique," IEEE 2021 International Conference on Advances in Computing, Communication and Control (ICAC3'21) 7th Edition (3rd and 4th December 2021), Mumbai, Maharashtra, India, December 03-04, 2021, pp. 1-6.

- [14]M. Saritha, Chelle Radhika, M. Narendra Reddy, M. lavanya, A. Karthik, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "Pipelined Distributive Arithmeticbased FIR Filter Using Carry Save and Ripple Carry Adder," Second IEEE International Conference on Communication, Computing and Industry 4.0 (C2I4-2021), Bengaluru, Karnataka, India, December 16-17, 2021, pp. 1-6.

- [15]S. Swathi, S. Sushma, V. Bindusree, L Babitha, Sukesh Goud. K, S. Chinavenkateswarlu, V. Vijay, Rajeev Ratna Vallabhuni, "Implementation of An Energy-Efficient Binary Square Rooter Using Reversible Logic By Applying The Non-Restoring Algorithm," Second IEEE International Conference on Communication, Computing and Industry 4.0 (C2I4-2021), Bengaluru, Karnataka, India, December 16-17, 2021, pp. 1-6.

- [16]Kiran, K. Uday, Gowtham Mamidisetti, Chandra shaker Pittala, V. Vijay, and Rajeev Ratna Vallabhuni, "A PCCN-Based Centered Deep Learning Process for Segmentation of Spine and Heart: Image Deep Learning," In Handbook of Research on Technologies and Systems for E-Collaboration During Global Crises, pp. 15-26. IGI Global, 2022.

- [17]Koteshwaramma, K. C., Vallabhuni Vijay, V. Bindusree, Sri Indrani Kotamraju, Yasala Spandhana, B. Vasu D. Reddy, Ashala S. Charan, Chandra S. Pittala, and Rajeev R. Vallabhuni, "ASIC Implementation of An Effective Reversible R2B Fft for 5G Technology Using Reversible Logic," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 5-13.

- [18]Vijay, Vallabhuni, Kancharapu Chaitanya, Chandra Shaker Pittala, S. Susri Susmitha, J. Tanusha, S. China Venkateshwarlu, and Rajeev Ratna Vallabhuni, "Physically Unclonable Functions Using Two-Level Finite State Machine," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 33-41.

- [19]Vijay, Vallabhuni, M. Sreevani, E. Mani Rekha, K. Moses, Chandra S. Pittala, KA Sadulla Shaik, C. Koteshwaramma, R. Jashwanth Sai, and Rajeev R. Vallabhuni, "A Review On N-Bit Ripple-Carry Adder, Carry-Select Adder And Carry-Skip Adder," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 27-32.

- [20] Vijay, Vallabhuni, Chandra S. Pittala, A. Usha Rani, Sadulla Shaik, M. V. Saranya, B. Vinod Kumar, RES Praveen Kumar, and Rajeev R. Vallabhuni, "Implementation of Fundamental Modules Using

Quantum Dot Cellular Automata," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 12-19.

- [21]Gollamandala Udaykiran Bhargava, Vasujadevi Midasala, and Vallabhuni Rajeev Ratna, "FPGA implementation of hybrid recursive reversable box filter-based fast adaptive bilateral filter for image denoising," Microprocessors and Microsystems, vol. 90, 2022, 104520.

- [22]Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, Vallabhuni Vijay, Usha Rani Anam, Kancharapu Chaitanya, "Numerical analysis of various plasmonic MIM/MDM slot waveguide structures," International Journal of System Assurance Engineering and Management, 2022.

- [23]Chandra Shaker Pittala, Vallabhuni Vijay, B. Naresh Kumar Reddy, "1-Bit FinFET Carry Cells for Low Voltage High-Speed Digital Signal Processing Applications," Silicon, 2022. https://doi.org/10.1007/s12633-022-02016-8.

- [24]M. Saritha, M. Lavanya, G. Ajitha, Mulinti Narendra Reddy, P. Annapurna, M. Sreevani, S. Swathi, S. Sushma, Vallabhuni Vijay, "A VLSI design of clock gated technique based ADC lock-in amplifier," International Journal of System Assurance Engineering and Management, 2022, pp. 1-8. https://doi.org/10.1007/s13198-022-01747-6

- [25]B. M. S. Rani, Vallabhuni Rajeev Ratna, V. Prasanna Srinivasan, S. Thenmalar, and R. Kanimozhi, "Disease prediction based retinal segmentation using bidirectional ConvLSTMU-Net," Journal of Ambient Intelligence and Humanized Computing, 2021, pp. 1-10. https://doi.org/10.1007/s12652-021-03017-y

- [26] Vallabhuni Vijay, C. V. Sai Kumar Reddy, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, M. Saritha, M. Lavanya, S. China Venkateswarlu and M. Sreevani, "ECG Performance Validation Using Operational Transconductance Amplifier with Bias Current," International Journal of System Assurance Engineering and Management, vol. 12, iss. 6, 2021, pp. 1173-1179.

- [27]K. C. Koteswaramma, Ande Shreya, N. Harsha Vardhan, Kantem Tarun, S. China Venkateswarlu, and Vallabhuni Vijay, "ASIC Implementation of division circuit using reversible logic gates applicable in ALUs," 1st International Conference on Innovations in Signal Processing and Embedded systems (ICISPES-2021), Hyderabad, India, October 22-23, 2021.

- [28] Vallabhuni Vijay, J. Sravana, K.S. Indrani, G. Ajitha,

A. Prashanth, K. Nagaraja, K.C. Koteswaramma, C.

Radhika, M. Hima Bindu, N. Manjula, "A SYSTEM

FOR CONTROLLING POSITIONING ACCORDING

TO MOVEMENT OF TERMINAL IN WIRELESS

COMMUNICATION BASED ON AI INTERFACE," The Patent Office Journal No. 50/2021, India. Application No. 202141055995 A.

- [29]Dr. L.V. Narasimha Prasad, Dr. Vijay Vallabhuni, Dr. S. China Venkateswarlu, Dr. V. Vhandra Jagan Mohan, Ms. P. Sruthilaya, Mr. K. Tarun Kumar, Mr. B. Raju, Mr. P. Ravinder, "Garbage Collector with Smart Segregation and Method of Segregation Thereof," The Patent Office Journal No. 04/2022, India. Application No. 202141062270 A.

- [30]Sravana, J., K. S. Indrani, M. Saranya, P. Sai Kiran, C. Reshma, and Vallabhuni Vijay, "Realisation of Performance Optimised 32-Bit Vedic Multiplier," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 14-21.

- [31] V. Vijay, J. Prathiba, S. Niranjan Reddy, V. Raghavendra Rao, "Energy efficient CMOS Full-Adder Designed with TSMC 0.18µm Technology," International Conference on Technology and Management (ICTM-2011), Hyderabad, India, June 8-10, 2011, pp. 356-361.

- [32] Vallabhuni Vijay, Pittala Chandra shekar, Shaik Sadulla, Putta Manoja, Rallabhandy Abhinaya, Merugu rachana, and Nakka nikhil, "Design and performance evaluation of energy efficient 8-bit ALU at ultra low supply voltages using FinFET with 20nm Technology," VLSI Architecture for Signal, Speech, and Image Processing, edited by Durgesh Nandan, Basant Kumar Mohanty, Sanjeev Kumar, Rajeev Kumar Arya, CRC press, 2021.

- [33] Vallabhuni Vijay, V.R. Seshagiri Rao, Kancharapu Chaitanya, S. China Venkateshwarlu, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, "High-Performance IIR Filter Implementation Using FPGA," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [34] Jujavarapu Sravana, S.K. Hima Bindhu, K. Sharvani, P. Sai Preethi, Saptarshi Sanyal, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "Implementation of Spurious Power Suppression based Radix-4 Booth Multiplier using Parallel Prefix Adders," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-6.

- [35]Chandra Shaker Pittala, Vallabhuni Vijay, A. Usha Rani, R. Kameshwari, A. Manjula, D.Haritha, Rajeev Ratna Vallabhuni, "Design Structures Using Cell Interaction Based XOR in Quantum Dot Cellular Automata," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [36]S. China Venkateshwarlu, Mohammad khadir, V. Vijay, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, "Optimized Design of Power Efficient FIR Filter Using Modified Booth Multiplier," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [37]G. Naveen, V.R Seshagiri Rao, Nirmala. N, Pavan kalyan. L, Vallabhuni Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Design of High-Performance Full Adder Using 20nm CNTFET Technology," 4th International Conference on Recent Trends in Computer Science and Technology

(ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [38] Mohammad khadir, S. Shakthi, S. Lakshmanachari, Vallabhuni Vijay, S. China Venkateswarlu, P. Saritha, Rajeev Ratna Vallabhuni, "QCA Based Optimized Arithmetic Models," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [39]P. Ashok Babu, P. Sridhar, and Rajeev Ratna Vallabhuni, "Fake Currency Recognition System Using Edge Detection," 2022 Interdisciplinary Research in Technology and Management (IRTM), Kolkata, India, February 24-26, 2022, pp. 1-5.