# Multiplier Design using Machine Learning Alogorithms for Energy Efficiency

Jane Juma<sup>1</sup>, R.M. Mdodo<sup>2</sup>, David Gichoya<sup>3</sup>

<sup>1-3</sup>Department of computing and information technology, kenyatta university, Nairobi, Kenya

#### KEYWORDS:

Cadence virtuoso; FinFET; Dynamic Logic; Domino logic; Manchester Carry Chain.

#### ARTICLE HISTORY:

Received 10.07.2022 Accepted 12.08.2022 Published 23.09.2022

DOI: https://doi.org/10.31838/jvcs/05.01.04

#### Abstract

Designers primary goal is to develop the Adder cell with improved performance viz. speed, fixed rise and fall time, as it the fundamental block in VLSI design process. The dynamic logic circuits are far better than the static logic circuits because it consumes less power and speed performance also increased. But, cascading of several blocks in dynamic logic is found to be a wrong analysis. This drawback of increased complexity with mismatched cascading is overcome by using domino logic circuits. By using domino logic circuits, the reduction of noise margins and increase the speed performance of the circuit is achieved. In this paper, domino logic based Manchester carry chain adder (MCC) is designed using FinFET 18nm technology in Cadence virtuoso. It is noticed that 4-bit and an 8-bit Manchester Carry Chain Adder (MCC) using domino logic design consumes less power and reduction in the delay of the proposed circuit compared with the previous architecture. Implementation results reveal that the 4-Bit MCC Adder has delay of 79.45% less compared to the existed standard design and power consumption also reduced to 94.15%.

Author's e-mail: jene.juma.j@gmail.com, mdodo.rm@gmail.com, david. gich@gmail.com

How to cite this article: Juma J, Mdodo RM, Gichoya D. Multiplier Design using Machine Learning Alogorithms for Energy Efficiency. Journal of Complementary Research, Vol. 5, No. 1, 2023 (pp. 28-34).

# INTRODUCTION

MCC Adder mainly work on *propagate* and *generate* signals. MCC uses *carry generate* and *carry propagate* signal to determine the carry for every stage. This *carry generate* and *carry propagate* signals are calculated in advance.<sup>[1-8]</sup> MCC requires a redundant stage to give input carry and also an input clock signal. In ripple-carry adder (RCA) architectures, the generated carry in first stage is passed to the next stage and up to N-stages.<sup>[9-14]</sup> The overall path delay of RCA is expressed mathematically as follows:

$$t_{delay} = t_{sum} + (N-1)t_{carry} \tag{1}$$

Where  $t_{carry}$  and  $t_{sum}$  are related to the propagation delays of sum and carry output from first stage to N-stages where N is the total number of stages of the adder module design. From the above equation (1), the majority of total delay of an adder circuit is contributed by  $t_{carry}$ . Thus, there is a need to reduce the delay belong to the carry generation path.<sup>[15-17]</sup> MCA optimizes the propagation delay related to carry path  $t_{carry}$ . Therefore, this carry chain improve the speed performance of the addition process of the overall adder block involved.<sup>[18-27]</sup> The functional verification of the adder blocks is validated with the following Table 1.

| Cin | В | А | Sum | Cout | Carry status |

|-----|---|---|-----|------|--------------|

| 1   | 1 | 1 | 1   | 1    | Generate     |

| 0   | 1 | 1 | 0   | 1    | Generate     |

| 1   | 0 | 1 | 0   | 1    | Propagate    |

| 0   | 0 | 1 | 1   | 0    | Propagate    |

| 1   | 1 | 0 | 0   | 1    | Propagate    |

| 0   | 1 | 0 | 1   | 0    | Propagate    |

| 1   | 0 | 0 | 1   | 0    | Delete       |

| 0   | 0 | 0 | 0   | 0    | Delete       |

The existing system of MCC adder is designed using CMOS at 180nm technology. The entire circuit design and simulation were done using cadence Tool. The existing MCC adder was designed using dynamic logic circuits. When the dynamic logic MCC adder is compared with the conventional logic circuit, the delay of the circuits is reduced but the power consumption was increased. The major drawback of the existing circuits is power consumption. The channel length is also large.<sup>[28-31]</sup>

The proposed system of 8-bit MCC adder is designed using FinFET at 18nm technology. The entire circuit design and simulation were done using cadence tool. The proposed circuit has many advantages like suppressed short channel effect, very less channel length, the delay of the circuit is optimized and power consumption is also reduced compared with the previous design.<sup>[32-39]</sup>

This paper is organized as follows; Section II describes the literature survey on FinFET transistors structural features followed by section III, which discuss about the proposed MCC Adder models. Section IV presents the cadence-based simulation results and their analysis. Section V elaborates the experimental findings of FinFET based MCC Adder. Section VI gives the conclusion of the paper including features and limitations followed by references.

## FUNDAMENTAL DESIGN ASPECTS OF FINFET

FinFET is the structural representation for fin shaped field effect transistor. Chenming Hu with support from his teammates has successfully modeled FinFET. The main objective behind the structure is having a thin body, then the gate capacitance is near to the channel .10nm or less than that width thin is the body. These leads to leakage path far away from the gate can effectively control the leakage.<sup>[32-35]</sup>

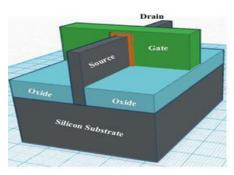

Bulk silicon or silicon on insulator (SOI) wafers are used for implementation of FinFET. The substrate consists of a thin fin of silicon body. The three sides of the channel are controlled due to wrapping of gate around the channel. The structure is said to be FinFET since Si body similar to the fish's back fin. The below Fig. 1 represents the 3-D model of FinFET structure.<sup>[16]</sup>

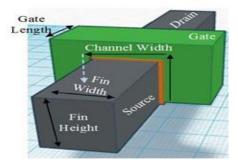

Bulk MOS has the channel which is horizontal. Where as in FinFET the Channel is vertical. Width of device is Height of the channel (Fin) in the FinFET. Perfect Width of Channel is given by

## *Width* $\oint$ *channel* = 2\* *Fin Height* + *Fin width*(2)

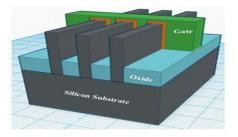

Increase in the height of the channel fin leads to increase in the width therefore leads to increase in the drive current of FinFET. Parallel construction of multiple fins connected together shown in Fig. 3 also leads to increase in the device drive current. Devices drive strength can be determined by varying channel width seen in Planar devices.<sup>[17-19]</sup>

Reduction in short channel effects and ensuring high  $V_t$  (Threshold) is seen in conventional MOS, where as in FinFET provides better SCE (Short Channel Effect), therefore doping of channel become optional this is due to wrapping of gate structure around the channel and body is thin. The fundamental variation of the MOSFET and FinFET is summarized in the Table 2.

## **PROPOSED ADDER MODELS**

## 8-Bit MCC Adder

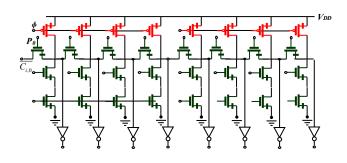

The 8-bit MCC Adder is applicable to optimize the delay and to increase the speed of the circuit. The 8-bit MCC Adder is mainly used instead of 4-bit MCC Adder as a building block, can lead to most efficient and high-speed adder implementation. The 8-bit MCC Adder consists of two 8-bit inputs namely  $P_{\gamma}$ ,

Fig. 1: 3-D model of FinFET structure

Fig. 2: Planar model of FinFET Structure.

Fig. 3: Multi-Fin structure.

| Table 2: Comparision | Table of | FinFET | and MOSFET |  |

|----------------------|----------|--------|------------|--|

|----------------------|----------|--------|------------|--|

| MOSFET                                                                          | FinFET                                                          |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Lower driven currents                                                           | Higher driven currents                                          |

| High leakage currents                                                           | Low leakage currents                                            |

| Short Channel Effect is present                                                 | Suppressed Short Channel Effect (SCE)                           |

| It consumes more power                                                          | It consumes less power                                          |

| Scaling and Mobility of tran-<br>sistor is not applicable for less<br>than 40nm | Scaling and Mobility of transistor is applicable less than 28nm |

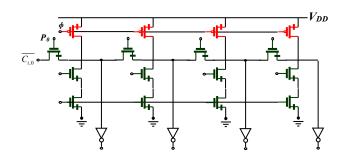

Fig. 4: 8-bit MCC Adder

P<sub>6</sub>, P<sub>5</sub>, P<sub>4</sub>, P<sub>3</sub>, P<sub>2</sub>, P<sub>1</sub>, P<sub>0</sub> and G<sub>7</sub>, G<sub>6</sub>, G<sub>5</sub>, G<sub>4</sub>, G<sub>3</sub>, G<sub>2</sub>, G<sub>1</sub>, G<sub>0</sub>. The clock signal is used control the entire operation of the circuit. The input values are getting from G<sub>i</sub> and P<sub>i</sub> of the *carry generate* and *carry propagate* signal. If CLK value is equal to logic '0' or LOW, then the circuit will be in the pre-charge state and it holds logic '0' for every output. If CLK value is change from LOW to HIGH then the output values will depends on the inputs. The inputs *carry generate* and *carry propagate* signal outputs from G<sub>i</sub> and P<sub>i</sub> and the corresponding carry output signals are C<sub>7</sub>, C<sub>6</sub>, C<sub>5</sub>, C<sub>4</sub>, C<sub>3</sub>, C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub>. The above Fig. 4 represents the 8-Bit MCC Adder [20]-[21].

The operation of 8-bit MCC Adder is same as the 4-bit MCC. The inputs of every stage Pi and Gi are

| $P_7 = A_7 \oplus B_7$ | $G_7 = A_7 \cdot B_7$                                                 |

|------------------------|-----------------------------------------------------------------------|

| $P_6 = A_6 \oplus B_6$ | $G_6 = A_6 \cdot B_6$                                                 |

| $P_5 = A_5 \oplus B_5$ | $G_{5} = A_{5} \cdot B_{5}$                                           |

| $P_4 = A_4 \oplus B_4$ | $\boldsymbol{G}_{4} = \boldsymbol{A}_{4} \cdot \boldsymbol{B}_{4}$    |

| $P_3 = A_3 \oplus B_3$ | $\boldsymbol{G}_3 = \boldsymbol{A}_3 \boldsymbol{.} \boldsymbol{B}_3$ |

| $P_2 = A_2 \oplus B_2$ | $\boldsymbol{G}_2 = \boldsymbol{A}_2 \cdot \boldsymbol{B}_2$          |

| $P_1 = A_1 \oplus B_1$ | $G_1 = A_1 \cdot B_1$                                                 |

| $P_o = A_o \oplus B_o$ | $\boldsymbol{G}_{o} = \boldsymbol{A}_{o} \cdot \boldsymbol{B}_{o}$    |

# 4-Bit MCC Adder

The Fig. 5 represents the 4-bit MCC Adder. It mainly has two 4-bit inputs namely  $G_3$ ,  $G_2$ ,  $G_1$ ,  $G_0$  and  $P_3$ ,  $P_2$ ,  $P_1$ ,  $P_0$ . For every stage, the inputs are getting from *carry propagate* and *carry generate* signal outputs. The clock signal controls the operation of the circuit. If clock signal equals to LOW or logic '0' then the circuit is in the pre-charge state and it holds logic '0' for every output. If clock value is change

Fig. 5: 4-bit MCC Adder

from logic '0' to logic '1', then the output is depends on the inputs. The *carry propagate* and *carry generate* inputs from first stage to fourth stage will possesses and corresponding carry outputs are generated namely  $C_3$ ,  $C_2$ ,  $C_1$ ,  $C_0$ .

In the figure 5, initial inputs are A, B and  $C_{in}$ .  $C_{in}$  must be always either logic '0' or logic '1' for the MCC. The inputs of  $P_i$  and  $G_i$  for every stage are

| $P_3 = A_3 \bigoplus B_3$ | $G_3 = A_3 \cdot B_3$ |

|---------------------------|-----------------------|

| $P_2 = A_2 \bigoplus B_2$ | $G_2 = A_2 \cdot B_2$ |

| $P_1 = A_1 \bigoplus B_1$ | $G_1 = A_1 \cdot B_1$ |

| $P_0 = A_0 \bigoplus B_0$ | $G_0 = A_0 \cdot B_0$ |

#### Case 1: When A=0 and B=0

If Clk=1,  $P=A \oplus B=0$  and G=A.B=0 then Cout =0.

In this case the output of P, G and Cout is always be logic '0'.

#### Case 2: When A=1 and B=0

If Clk=1, P=A⊕B=1 and G=A.B=0

In this case the propagation P output is equal to '1' then  $C_{out}=C_{in}$  i.e., the input of carry is straightly moving to the output of carry. The circuit is in carry propagation state.

#### Case 3: When A=1 and B=0

If Clk=1, P=A⊕B=1 and G=A.B=0

In this case the propagation P output is equal to '1' then  $C_{out}$ =Cin i.e., the input of carry is straightly moving to the output of carry. The circuit is in carry propagation state.

#### Case 4: When A=1 and B=1

If Clk=1, P=A⊕B=0 and G=A.B=1

In this case the generation G output is equal to '1' then  $C_{out}=1$ . The circuit is in carry generation state.

In all the above cases, when Clk='0' the carry output  $C_{out}=0$ . The same analogy is applicable for both 8-bit and 4-bit MCC adders.

## **OUTCOMES OF THE STANDARD MODELS**

## 4-Bit MCC Adder

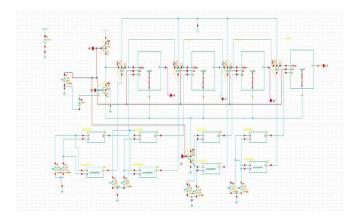

The MCC adder of 4-bit capacity is designed using FinFET nodes and the same has presented in the Fig. 6. The required configurations corresponding to inverter modules

too has designed using the same FinFET models. Similarly, the propagation and generation signal symbol are created which has multiple number of n-LVT and p-LVT.

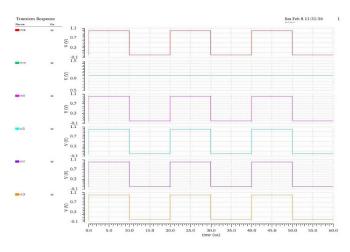

## Transient response of 4-Bit MCC adder

The response of a system to a change from a steady state or equilibrium state is known as Transient response. The transient is not definitely tied to *on* or *off* state, but to any state that affects the steady state of the system.

The schematic diagrams or circuit design of 4-bit and 8-bit MCC Adder are simulated using Cadence software and FinFET 18nm technology to obtain transient response.

From the transient response figures, 0V represents logic '0' which implies 'OFF' state and where as 1V represents logic '1' which implies 'ON' state.

In FinFET, the maximum voltage is considered up to 1V. This means that  $V_{DD}$  is 1V and GND is 0V. FinFET cannot withstand high voltages that are greater than 1V as it leads to the damage of transistors.

The Fig. 7 represents the transient response of 4-bit MCC Adder. The entire simulation is done using Cadence virtuoso at FinFET 18nm technology.

Fig. 6: Schematic diagram of 4-bit MCC Adder.

Fig. 7: Transient response of 4-bit MCC Adder.

#### **EXPERIMENTAL FINDINGS**

Using Cadence virtuoso FinFET 18nm spectre models, the following outcomes for 4-bit MCC Adders are observed.

## Delay Metric

It is observed from the above delay analysis Table 3, the propagation delay of the proposed design has the considerable impact of delay reduction. The proposed design has reduced delay value of 0.1013ns. When compared with previous design of 4-bit MCC Adder, the proposed model has reduced delay of about 80% less.

#### Power Metric

From the Table 4, the power consumption of the proposed circuit is also reduced. The proposed design has reduced power consumption value of 1.005uW. When compared with previous standard design, the energy dissipation for the design of the circuit shown in Fig. 6 is reduced by 94.15%.

The PDP values presented in the above Table V shows the reduction of the PDP metric compare to that of previous standard models. PDP for the design of Fig. 6 is reduced by 98.79% to the original conventional MOS transistor version.

It can be noticed from the above EDP analysis Table VI, hence from previous delay and PDP measures too, even EDP also has the proportionate minimized value. When compared with previous standard design, the EDP for the design of Fig. 6 is reduced by 99.75%.

| Existing design                 | Proposed design                              |                     |

|---------------------------------|----------------------------------------------|---------------------|

| (4-Bit MCC Adder)               | (4-Bit MCC Adder)                            | Change in delay (%) |

| 0.493ns                         | 0.1013ns                                     | 79.45%              |

|                                 |                                              | Decrease            |

| Table 4: Pov                    | wer Analysis Table for 4-                    |                     |

| Table 4: Pov<br>Existing design | wer Analysis Table for 4-<br>Proposed design |                     |

|                                 |                                              | bit MCC Adder       |

| Existing design                 | Proposed design                              |                     |

| Table 5: PDP Analysis Table for 4-bit MCC Adder |

|-------------------------------------------------|

|-------------------------------------------------|

| Existing design   | Proposed design   | Change in PDP (%) |

|-------------------|-------------------|-------------------|

| (4-Bit MCC Adder) | (4-Bit MCC Adder) |                   |

| 8.47*10-15J       | 1.02*10-16J       | 98.79%            |

|                   |                   | Decrease          |

| Table 6: EDP Analysis Table for 4-bit MCC Adder |

|-------------------------------------------------|

|-------------------------------------------------|

| Existing design<br>(4-Bit MCC Adder) | Proposed design<br>(4-Bit MCC Adder) | Change in EDP (%) |

|--------------------------------------|--------------------------------------|-------------------|

| 4.175*10-24Js                        | 1.033*10-26Js                        | 99.75%            |

|                                      |                                      | Decrease          |

# CONCLUSION

Cadence virtuoso is used to design and simulate the MCC circuits. There is an excellent improvement in reduction of the power consumption and delay of the proposed circuit and the performance and speed of the circuit is increased. The performance is analysed by using 18nm FinFET spectre models. The simulation results demonstrates reduced power consumption and delay values of 4-bit and 8-bit MCC Adders. The reduced power and delay values of 4-bit MCC adder are 1.005uW and 0.1013ns, respectively. When compared with previous design of 4-bit MCC Adder, the delay of the proposed FinFET based circuit reduced by 79.45%. It also observed that the power consumption of 4-bit MCC Adder compared with previous design is reduced by 94.15%. Hence, the proposed 4-bit and 8-bit MCC Adders are highly efficient compared with the previous design. As a further work minimization of the distortions through various combinations of logics and designing the MCC adders for complex circuits or higher variables like 16, 32, 64 bit can be done. The paper further extended by reducing the channel length or designing in submicron technology and decreasing the area of this chain.

# REFERENCES

- [1] Amelifard, Behnam, Farzan Fallah, and Massoud Pedram, "Leakage minimization of SRAM cells in a dual-Vt and dual-Tox technology," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 16, np. 7, 2008, pp. 851-859.

- [2] Ratna, Vallabhuni Rajeev, and Ramya Mariserla. "Design and Implementation of Low Power 32-bit Comparator." (2021).

- [3] Vallabhuni Vijay, Kancharapu Chaitanya, T. Sai Jaideep, D. Radha Krishna Koushik, B. Sai Venumadhav, Rajeev Ratna Vallabhuni, "Design of Optimum Multiplexer In Quantum-Dot Cellular Automata," International Conference on Innovative Computing, Intelligent Communication and Smart Electrical systems (ICSES -2021), Chennai, India, September 24-25, 2021.

- [4] S. Sushma, S. Swathi, V. Bindusree, Sri Indrani Kotamraju, A. Ashish Kumar, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "QCA Based Universal Shift Register using 2 to 1 Mux and D flip-flop," IEEE 2021 International Conference on Advances in Computing, Communication and Control (ICAC3'21) 7th Edition (3rd and 4th December 2021), Mumbai, Maharashtra, India, December 03-04, 2021, pp. 1-6.

- [5] Bandi Mary Sowbhagya Rani, Vasumathi Devi Majety, Chandra Shaker Pittala, Vallabhuni Vijay, Kanumalli Satya Sandeep, Siripuri Kiran, "Road Identification Through Efficient Edge Segmentation Based on Morphological Operations," Traitement du Signal, vol. 38, no. 5, Oct. 2021, pp. 1503-1508.

- [6] M. Lavanya, Malla Jyothsna Priya, Ponukumatla Janet, Kavuluri Pavan Kalyan, and Vijay Vallabhuni, "Advanced 18nm FinFET Node Based Energy Efficient and High-Speed Data Comparator using SR Latch," International Conference On Advances In Signal Processing And Communication

Engineering (ICASPACE 2021), Hyderabad, India, July 29-31, 2021.

- [7] J. Sravana, K.S. Indrani, Sankeerth Mahurkar, M. Pranathi, D. Rakesh Reddy, and Vijay Vallabhuni, "Optimised VLSI Design of Squaring Multiplier using Yavadunam Sutra through Deficiency Bits Reduction," International Conference On Advances In Signal Processing And Communication Engineering (ICASPACE 2021), Hyderabad, India, July 29-31, 2021.

- [8] L. Babitha, U. Somanaidu, CH. Poojitha, K. Niharika, V. Mahesh, and Vallabhuni Vijay, "An Efficient Implementation of Programmable IIR Filter for FPGA," 1st International Conference on Innovations in Signal Processing and Embedded systems (ICISPES-2021), Hyderabad, India, October 22-23, 2021.

- [9] K. C. Koteswaramma, Ande Shreya, N. Harsha Vardhan, Kantem Tarun, S. China Venkateswarlu, and Vallabhuni Vijay, "ASIC Implementation of division circuit using reversible logic gates applicable in ALUs," 1st International Conference on Innovations in Signal Processing and Embedded systems (ICISPES-2021), Hyderabad, India, October 22-23, 2021.

- [10] M. Sreevani, S. Lakshmanachari, B. Manvitha, Y.J.N. Pravalika, T.Praveen, V.Vijay, Rajeev Ratna Vallabhuni, "Design of Carry Select Adder Using Logic Optimization Technique," IEEE 2021 International Conference on Advances in Computing, Communication and Control (ICAC3'21) 7th Edition (3rd and 4th December 2021), Mumbai, Maharashtra, India, December 03-04, 2021, pp. 1-6.

- [11] M. Saritha, Chelle Radhika, M. Narendra Reddy, M. lavanya, A. Karthik, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "Pipelined Distributive Arithmetic-based FIR Filter Using Carry Save and Ripple Carry Adder," Second IEEE International Conference on Communication, Computing and Industry 4.0 (C2I4-2021), Bengaluru, Karnataka, India, December 16-17, 2021, pp. 1-6.

- [12] S. Swathi, S. Sushma, V. Bindusree, L Babitha, Sukesh Goud. K, S. Chinavenkateswarlu, V. Vijay, Rajeev Ratna Vallabhuni, "Implementation of An Energy-Efficient Binary Square Rooter Using Reversible Logic By Applying The Non-Restoring Algorithm," Second IEEE International Conference on Communication, Computing and Industry 4.0 (C2I4-2021), Bengaluru, Karnataka, India, December 16-17, 2021, pp. 1-6.

- [13] S. Swathi, S. Sushma, C. Devi Supraja, V. Bindusree, L. Babitha and Vallabhuni Vijay, "A Hierarchical Image Matting Model for Blood Vessel Segmentation in Retinal Images," International journal of system assurance engineering and management, vol. 13, iss. 3, 2022, pp. 1093-1101.

- [14] Vallabhuni Vijay, Pittala Chandra shekar, Shaik Sadulla, Putta Manoja, Rallabhandy Abhinaya, Merugu rachana, and Nakka nikhil, "Design and performance evaluation of energy efficient 8-bit ALU at ultra low supply voltages using FinFET with 20nm Technology," VLSI Architecture for Signal, Speech, and Image Processing, edited by Durgesh Nandan, Basant Kumar Mohanty, Sanjeev Kumar, Rajeev Kumar Arya, CRC press, 2021.

- [15] Kiran, K. Uday, Gowtham Mamidisetti, Chandra shaker Pittala, V. Vijay, and Rajeev Ratna Vallabhuni, "A PCCN-Based Centered Deep Learning Process for Segmentation

32

of Spine and Heart: Image Deep Learning," In Handbook of Research on Technologies and Systems for E-Collaboration During Global Crises, pp. 15-26. IGI Global, 2022.

- [16] Vallabhuni Vijay, V.R. Seshagiri Rao, Kancharapu Chaitanya, S. China Venkateshwarlu, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, "High-Performance IIR Filter Implementation Using FPGA," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [17] Jujavarapu Sravana, S.K. Hima Bindhu, K. Sharvani, P. Sai Preethi, Saptarshi Sanyal, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "Implementation of Spurious Power Suppression based Radix-4 Booth Multiplier using Parallel Prefix Adders," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-6.

- [18] Chandra Shaker Pittala, Vallabhuni Vijay, A. Usha Rani, R. Kameshwari, A. Manjula, D.Haritha, Rajeev Ratna Vallabhuni, "Design Structures Using Cell Interaction Based XOR in Quantum Dot Cellular Automata," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [19] S. China Venkateshwarlu, Mohammad khadir, V. Vijay, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, "Optimized Design of Power Efficient FIR Filter Using Modified Booth Multiplier," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [20] G. Naveen, V.R Seshagiri Rao, Nirmala. N, Pavan kalyan. L, Vallabhuni Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Design of High-Performance Full Adder Using 20nm CNTFET Technology," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [21] Mohammad khadir, S. Shakthi, S. Lakshmanachari, Vallabhuni Vijay, S. China Venkateswarlu, P. Saritha, Rajeev Ratna Vallabhuni, "QCA Based Optimized Arithmetic Models," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [22] P. Ashok Babu, P. Sridhar, and Rajeev Ratna Vallabhuni, "Fake Currency Recognition System Using Edge Detection," 2022 Interdisciplinary Research in Technology and Management (IRTM), Kolkata, India, February 24-26, 2022, pp. 1-5.

- [23] Koteshwaramma, K. C., Vallabhuni Vijay, V. Bindusree, Sri Indrani Kotamraju, Yasala Spandhana, B. Vasu D. Reddy, Ashala S. Charan, Chandra S. Pittala, and Rajeev R. Vallabhuni, "ASIC Implementation of An Effective Reversible R2B Fft for 5G Technology Using Reversible Logic," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 5-13.

- [24] Vijay, Vallabhuni, Kancharapu Chaitanya, Chandra Shaker Pittala, S. Susri Susmitha, J. Tanusha, S. China Venkateshwarlu, and Rajeev Ratna Vallabhuni, "Physically Unclonable Functions Using Two-Level Finite State Machine," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 33-41.

- [25] Vijay, Vallabhuni, M. Sreevani, E. Mani Rekha, K. Moses, Chandra S. Pittala, KA Sadulla Shaik, C. Koteshwaramma, R. Jashwanth Sai, and Rajeev R. Vallabhuni, "A Review On N-Bit Ripple-Carry Adder, Carry-Select Adder And Carry-Skip Adder," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 27-32.

- [26] Vallabhuni Vijay, J. Sravana, K.S. Indrani, G. Ajitha, A. Prashanth, K. Nagaraja, K.C. Koteswaramma, C. Radhika, M. Hima Bindu, N. Manjula, "A SYSTEM FOR CONTROLLING POSITIONING ACCORDING TO MOVEMENT OF TERMINAL IN WIRELESS COMMUNICATION BASED ON AI INTERFACE," The Patent Office Journal No. 50/2021, India. Application No. 202141055995 A.

- [27] Dr. L.V. Narasimha Prasad, Dr. Vijay Vallabhuni, Dr. S. China Venkateswarlu, Dr. V. Vhandra Jagan Mohan, Ms. P. Sruthilaya, Mr. K. Tarun Kumar, Mr. B. Raju, Mr. P. Ravinder, "Garbage Collector with Smart Segregation and Method of Segregation Thereof," The Patent Office Journal No. 04/2022, India. Application No. 202141062270 A.

- [28] Sravana, J., K. S. Indrani, M. Saranya, P. Sai Kiran, C. Reshma, and Vallabhuni Vijay, "Realisation of Performance Optimised 32-Bit Vedic Multiplier," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 14-21.

- [29] V. Vijay, J. Prathiba, S. Niranjan Reddy, V. Raghavendra Rao, "Energy efficient CMOS Full-Adder Designed with TSMC 0.18µm Technology," International Conference on Technology and Management (ICTM-2011), Hyderabad, India, June 8-10, 2011, pp. 356-361.

- [30] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Optimal design of VLSI implemented Viterbi decoding," National conference on Recent Advances in Communications & Energy Systems, (RACES-2011), Vadlamudi, India, December 5, 2011, pp. 67-71.

- [31] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Low power based optimal design for FPGA implemented VMFU with equipped SPST technique," National Conference on Emerging Trends in Engineering Application (NCE-TEA-2011), India, June 18, 2011, pp. 224-227.

- [32] Vallabhuni Vijay, and Avireni Srinivasulu, "A Novel Square Wave Generator Using Second Generation Differential Current Conveyor," Arabian Journal for Science and Engineering, vol. 42, iss. 12, 2017, pp. 4983-4990.

- [33] Vijay, Vallabhuni, Chandra S. Pittala, A. Usha Rani, Sadulla Shaik, M. V. Saranya, B. Vinod Kumar, RES Praveen Kumar, and Rajeev R. Vallabhuni, "Implementation of Fundamental Modules Using Quantum Dot Cellular Automata," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 12-19.

- [34] Gollamandala Udaykiran Bhargava, Vasujadevi Midasala, and Vallabhuni Rajeev Ratna, "FPGA implementation of hybrid recursive reversable box filter-based fast adaptive bilateral filter for image denoising," Microprocessors and Microsystems, vol. 90, 2022, 104520.

- [35] Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, Vallabhuni Vijay, Usha Rani Anam, Kancharapu Chaitanya, "Numerical analysis of various plasmonic MIM/MDM slot waveguide structures," International Journal of System Assurance Engineering and Management, 2022.

- [36] Chandra Shaker Pittala, Vallabhuni Vijay, B. Naresh Kumar Reddy, "1-Bit FinFET Carry Cells for Low Voltage High-

Journal of VLSI circuits and systems, , ISSN 2582-1458

Speed Digital Signal Processing Applications," Silicon, 2022. https://doi.org/10.1007/s12633-022-02016-8.

- [37] M. Saritha, M. Lavanya, G. Ajitha, Mulinti Narendra Reddy, P. Annapurna, M. Sreevani, S. Swathi, S. Sushma, Vallabhuni Vijay, "A VLSI design of clock gated technique based ADC lock-in amplifier," International Journal of System Assurance Engineering and Management, 2022, pp. 1-8. https://doi.org/10.1007/s13198-022-01747-6

- [38] B. M. S. Rani, Vallabhuni Rajeev Ratna, V. Prasanna Srinivasan, S. Thenmalar, and R. Kanimozhi, "Disease pre-

diction based retinal segmentation using bi-directional ConvLSTMU-Net," Journal of Ambient Intelligence and Humanized Computing, 2021, pp. 1-10. <u>https://doi.org/10.1007/s12652-021-03017-y</u>

[39] Vallabhuni Vijay, C. V. Sai Kumar Reddy, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, M. Saritha, M. Lavanya, S. China Venkateswarlu and M. Sreevani, "ECG Performance Validation Using Operational Transconductance Amplifier with Bias Current," International Journal of System Assurance Engineering and Management, vol. 12, iss. 6, 2021, pp. 1173-1179.