# CSA Implementation Using Novel Methodology: RTL Development

Kriti S. Chakma<sup>1</sup>, Md. Sarwar U. Chowdhury<sup>2</sup>

<sup>1,2</sup>Department of Electrical and Electronic Engineering, International Islamic University Chittagong, Chittagong 4318, Bangladesh

#### **KEYWORDS:**

Area Delay Product (ADP); CSLA; Power Delay Product (PDP); ZFCLOT.

#### **ARTICLE HISTORY:**

Received 14.07.2022 Accepted 15.08.2022 Published 27.09.2022

DOI: https://doi.org/10.31838/jvcs/05.02.04

#### ABSTRACT

Carry Select Adder (CSLA) is an essentially utilized adder on account of its higher computational speed. CSLA is utilized in the space of incorporation frameworks. This paper proposes a CSLA design by carrying out the Logic Optimization Technique (ZFCLOT) using Zero Finding Logic contrasted with ordinary Zero Finding Logic (ZFC). This paper notices the different presentation measurements like area, power, delay, area delay product (ADP), power delay product (PDP) and effectiveness. Approval of the ZFCLOT put together CSLA is displayed with respect to Cadence stage utilizing 45 nm platform. The presented CSLA utilizing ZFCLOT has shown advanced execution measurements, explicitly, region and power improvement of 47.287% and 49.1%, separately contrasted with the current standard plans.

Author's e-mail: Chakma.ks@gmail.com, Chowdhury.uds@gmail.com

How to cite this article: Chakma KS, Chowdhury MSU. CSA Implementation Using Novel Methodology: RTL Development. Journal of Complementary Research, Vol. 5, No. 2, 2023 (pp. 22-28).

# INTRODUCTION

In the present digitalized world, there is critical significance in planning, acknowledging and carrying out the structures of circuits to perform paired expansion and improve the presentation of different cut off points in computerized signal applications like Processing of signal in digital industry and Processing of signals in biomedical industry. The speed of a particular plan is by and large dictated by the critical path delay (CPD). Ripple carry adder (RCA) is utilized to duplicate full adders which, is executed in a course technique. CPD for such kind of RCA adder restricts the speed of the framework.<sup>[1-10]</sup>

A carry select adder (CSLA) is utilized to diminish this presentation metric, for example CPD. One of the productive plans to improve the speed of multi-bit adders is Square Root (SQRT)- CSLA.<sup>[1]</sup> CSLA is planned by utilizing two RCAs, in which each has input carry 0 and 1, separately; as indicated by the forming carry input, the exact whole and carry yield is chosen. The expense of the chip is chosen by the adder plan. Thus, the cost will likewise be diminished when the space of a particular plan is decreased.<sup>[11-20]</sup> Customary CSLA is quicker than RCA, however quite possibly the most and basic execution measurements, an area that influences the plan cost. The Logic streamlining procedure diminishes the region where rationale is addressed without changing its comparable recurrence. Different Logic enhancements have been performed to diminish an area by utilizing a circuit with an expansion in CPD.<sup>[21-28]</sup>

To advance the region, in CSLA the Zero Finding Logic (ZFC) is used as the development for the reason to optimize the area.<sup>[2]</sup> The combinational postponement is expanded due to the utilization of XOR & AND entryways.<sup>[29-35]</sup> By altering the ripple carry adder for improving region, CSLALOT is planned.<sup>[3]</sup> However, the speed of the engineering is decreased by the use of countless gatherings. Planned CSLA designs by utilizing circuit improvements and rationale advancement strategies for speed, region and power productivity.<sup>[4]</sup> All these presentation measurements can't be tended at a time. In this way CSLA is planned by utilizing NAND entryways and additionally entryways to achieve fast.<sup>[36-43]</sup>

However, the development possesses added region when contrasted with CSLA planned by bit-cut squares. In this paper, CSLA utilizing altered ZFC that is ZFCLOT is designed to diminish the region. The proposed architecture results and correlations are described in Section 4. At last, conclusion is given in Section 5.

## **PROPOSED MODELS**

## **Architecture of Zfclot**

The design and construction of CSLA using ZFCLOT are implemented by utilizing the technique of logic optimization. The construction of ZFCLOT of CSLA consists the quantity of eight modules. Table 1 shows the designs utilized in ZFCLOT of CSLA. As the module size rises, extra half adders are required, that in turn decreases the area.<sup>[46-58]</sup>

### Ripple Carry Adder using two full adders (RCA)

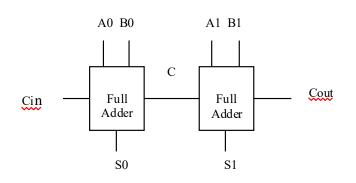

This is one of the internal module used in the implementation of CSLA. It comprises of two full adders. The main full adder has three inputs as A0, B0 and Cin. Now, the outputs of first full adder has a sum S0 and a carry C which is taken as one of the input to the second full adder along with A1 and B1. At last, the final outputs obtained are S1 and Cout as shown in Fig. 1.

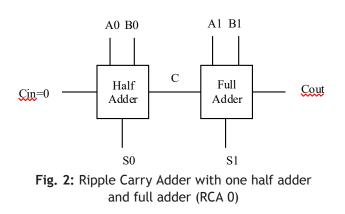

# Ripple Carry Adder with one half adder and full adder (RCA 0)

This is also one of the internal module used in the implementation of CSLA. It consists of one full adder and

TABLE 1: Modules used for designing CSLA

Module

Set 1

Set 2

Module 0

Ripple Carry Adder with carry

Module 1 - Module 7

Ripple Carry Adder with 0 carry

ZFCLOT

Fig. 1: Ripple Carry Adder using two full adders (RCA)

one half adder. The half adder has two inputs as A0, B0. Here, we consider Cin as 0. Now, the outputs of half adder has a sum S0 and a carry C which is taken as one of the input to the full adder along with A1 and B1. At last, the final outputs obtained are S1 and Cout as shown in Fig. 2.

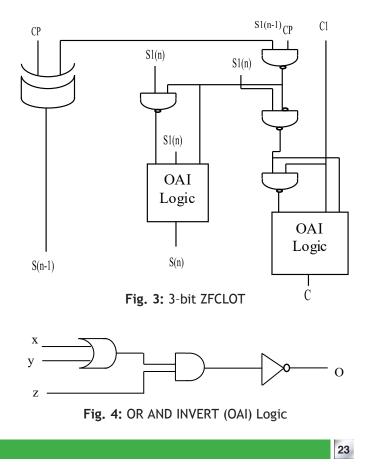

## 3 – bit ZFCLOT

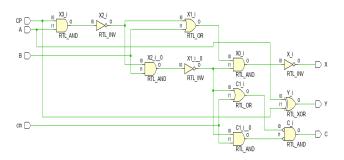

Every module has two information inputs. 16-bit information modules are isolated such that each gathering has two information inputs. Alongside the information inputs, each gathering has either input carry cin or carry before carry CP. Module 0 comprises of a 2-cycle RCA. Module 1 to Module 7 comprises of RCA 0 and ZFCLOT. The development for Zero Finding Logic of 3-bit utilizing logic enhancement technique (ZFCLOT) is appeared in fig.3. NAND entryway utilizes low region and furthermore devours less power contrasted with XOR - entryway [6][7]. Subsequently to diminish the region and power utilization, ZFCLOT is planned utilizing NAND entryways. Here, the execution of CSLA utilizing ZFCLOT is animated utilizing the 45 nm Cadence devices. OR AND INVERT (OAI) Logic is used as one of the parts in designing 3 - bit ZFCLOT.

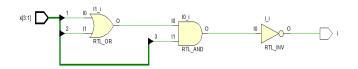

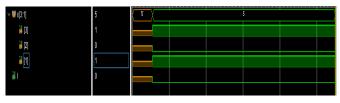

In this logic, the first two inputs which are named as x and y are given as inputs to OR entryway. Now, the output obtained at the OR entryway is given as input to AND entryway along with the third input which is named as z. The output obtained at the AND entryway is passed to a NOT entryway where the output is inverted and finally the output is O as shown in the Fig. 4.

### RESULTS

The CSLA of 16 - bit utilizing ZFCLOT is carried out utilizing RCA of 2 - bit which has two full adders, a 2 - bit RCA 0, which has one-half adder and one full adder, a 3 - bit ZFCLOT circuit appeared in Fig. 3 and lastly 2:1 multiplexer. The activity of the circuits which are referenced above is recreated. The outcomes are noticed, checked and the outcome is as a waveform as demonstrated in the beneath pictures, and furthermore the circuit is being seen by RTL (Schematic Capture) as demonstrated in the below figures. There are two 16 - bit inputs, one carry input, one 16 - bit yield and a carry yield acquired at long last.

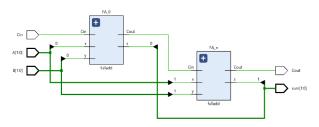

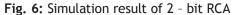

The 2 - bit RCA design is demonstrated in fig.5. It has two full adders named FA\_0 and FA\_n. 'A' and 'B' are the 2 - bit sources of info and Cin is the information carry, and Cout is the yield carry of 1 - bit, and 'sum' is the 2 - bit yield acquired after reproduction. The different blends for A, B and Cin are taken, and the yields Cout and total are as demonstrated in the fig. 6

The 2 - bit RCA 0 design is demonstrated in the fig. 7. RCA 0 is a circuit wherein the carry input is taken as '0'. It has one-half adder and one full adder named ha and fa. A and B are the 2 - bit contributions of a half adder, and ca, s are the comparing yields of half adder and these yields of half adder are given as contributions to the full adder. Presently, the full adder has inputs cin, x, y while the last

Fig. 5: Schematic capture of 2 - bit RCA

Fig. 7: Schematic Capture of 2 - bit RCA0

yields got are c1, which is the carry yield and sum is the 2 - bit yield. The numerous mixes for A, B are taken and the yields 'c1' and sum are as demonstrated in the Fig. 8.

One of the principal blocks utilized in the CSLA utilizing ZFCLOT is 3 - bit "OAI Logic". In this rationale, the initial two sources of info are gone through an OR entryway, and afterward the yield got here, and the third information is being passed to AND entryway, lastly, the yield here is transformed. It has three contributions as x(1), x(2) and x(3), as demonstrated in the fig. 9. For different mixes of sources of info, the yields are plotted as a waveform, as demonstrated in the Fig. 10.

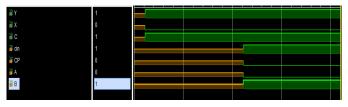

In ZFCLOT, A, B are taken as sources of info and cin is likewise taken as one of the information CP is the previous carry. ZFCLOT is carried out utilizing NAND entryways and OAI Logic (Or And Invert Logic). X, Y, and C are the resulting yields as shown in the fig. 11. The different blends of A, B, and cin are taken, and the outcome is a waveform as demonstrated in the Fig. 12.

The Schematic Capture of CSLA utilizing ZFCLOT is as demonstrated in Fig. 8. This is carried out and orchestrated utilizing 45 nm Cadence innovation instruments. Here, there is a carry information and two 16 - bit inputs. ZFCLOT is acquired by interfacing the RCA, RCA 0 and ZFCLOT segments with the assistance of a 2:1 multiplexer. At last, the outcomes acquired is a 16 - bit yield vector and a got carry. There are different components present in the Cadence technology. The below Table 3 shows the space occupied by each item in 45 nm Cadence platform.

Fig. 8: Simulation result of 2 bit - RCA0

Fig. 9: Schematic Capture of OAI Logic

Fig. 10: Simulation waveform of OAI Logic

Module 0 has a ripple carry adder with two full adders and also another adder with one half adder and full adder. The below table 4 shows the space occupied by these two adders theoretically. The total space occupied by these two adders is about  $384.7522 \ \mu m^2$ .

Dynamic and Leakage power are the main rule segments for complete power use. NAND entryway uses fewer semiconductors when appeared differently in relation to XOR & AND entrances. Thus, supreme power use is lessened. Application - Specific Integrated Circuit (ASIC) approach is utilized for acquiring the 3 - bit ZFCLOT. Various strategies are mulled over like Square Root CSLA, Square Root Binary to Excess CSLA converter, Square Root Zero Finding Logic CSLA, CSLALOT and ZFCLOT utilizing CSLA. These outcomes are recreated and are organized as demonstrated in the Table 4.

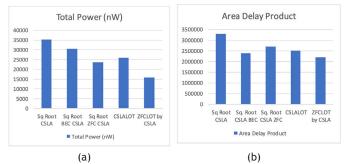

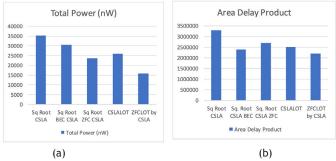

Fig. 13 shows the Dynamic Power comparison for various designs like Square Root CSLA, Square Root BEC CSLA, Square Root Zero Finding Logic CSLA, CSLALOT and ZFCLOT by CSLA. The designed Square Root CSLA (Sq Root CSLA), Square Root Binary to Excess Converter CSLA (Sq Root BEC CSLA) models by utilizing half adder and AND entryways. This half adder being planned by utilizing XOR entryways, AND entryways that involves high region and furthermore devours high power.

Fig. 11: Schematic Capture of a 3 - bit ZFCLOT

Fig. 12: Simulation waveform of a 3 - bit ZFCLOT

Full adder configuration assumes a vital part in the plan of all previously specified designs. According different investigations, it has been seen that different improvements have been acted in the perspective on full adder. In this manner, the full adder which consists of least region is given as an essential structure block in Cadence device library and utilized in plan of ZFCLOT by CSLA.

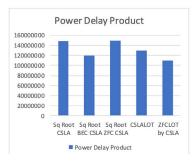

As examined before, a portion of the advanced parts are utilized in the plan of ZFCLOT by CSLA. Subsequently, Power Leakage, Dynamic Power and all out other powers are decreased. Fig. 14 shows the Leakage Power comparison for different designs like mentioned before. Fig. 15 shows the entire power correlation for various plans that is acquired by the addition of the spillage and the dynamic power. It is hard to lessen entire presentation measurements like space occupancy, power, and retardation. There should be compromise between space occupancy, power and retardation. Accordingly in the planned engineering, region and power improvements are done which expands defer which is the significant restriction for this design. Delay Products of Area and Power i.e. ADP and PDP are utilized to check the general exhibition of the engineering. ADP is acquired through increasing delay of area. Essentially, PDP is acquired through duplicating delay of power. Fig. 16 shows the Product Delay of Area (ADP). Fig. 17 shows the

TABLE 2: Key digital elements in 45 nm Cadence Technology

| Space occupied (µm2) |

|----------------------|

|                      |

| 3.489                |

| 3.489                |

| 6.258                |

| 4.572                |

| 2.874                |

| 8.4736               |

| 3.147                |

| 15.8756              |

|                      |

TABLE 3: Theoretical Space Occupancy of CSLALOT

| Ripple Carry Adder with two full | Ripple Carry Adder with one half         |

|----------------------------------|------------------------------------------|

| adders                           | adder and one full adder                 |

| It comes under Module 0          | It comes under Module 1 to Mod-<br>ule 7 |

| The Space occupied is 26.8745    | The Space occupied is 357.8777           |

|                                  |                                          |

|  | TABLE 4: ASIC | outcomes | utilizing | Cadence | 45 nn | n platform |

|--|---------------|----------|-----------|---------|-------|------------|

|--|---------------|----------|-----------|---------|-------|------------|

| Space Occupied (µm2) | Time Delay (ns)                                                  | Power Consumption (nW)                                                                                                                                                   |  |  |  |  |

|----------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 864.259              | 2968                                                             | 35213.52                                                                                                                                                                 |  |  |  |  |

| 582.936              | 3654                                                             | 30447.29                                                                                                                                                                 |  |  |  |  |

| 568.412              | 5159                                                             | 23593.605                                                                                                                                                                |  |  |  |  |

| 600.149              | 4527                                                             | 25863.249                                                                                                                                                                |  |  |  |  |

| 410.268              | 5219                                                             | 15874.204                                                                                                                                                                |  |  |  |  |

|                      | Space Occupied (μm2)<br>864.259<br>582.936<br>568.412<br>600.149 | Space Occupied (µm2)         Time Delay (ns)           864.259         2968           582.936         3654           568.412         5159           600.149         4527 |  |  |  |  |

Journal of VLSI circuits and systems, , ISSN 2582-1458

Fig. 13: Dynamic power comparison for various designs. Leakage Power comparison for various designs

Fig. 15: PDP Comparison for different designs

Product Delay of Power (PDP). The above mentioned two delays, the CSLA utilizing ZFCLOT is low when contrasted with a condition to workmanship structures.

#### CONCLUSION

From this paper, we conclude that the VLSI construction is planned, recreated, and integrated utilizing Cadence platform for CSLA utilizing ZFCLOT. This design achieves the performance of area as 47.287% when contrasted with Sq Root CSLA. This design also achieves the performance of power as 49.1% when contrasted with Sq Root CSLA. This design also achieves the performance of area as 28.954% when contrasted with Sq Root BEC CSLA. This also achieves the performance of power as 36.2% when contrasted to Sq Root BEC CSLA. This design also achieves the performance of area as 16.424% and the performance of power as 14.459% when contrasted with Sq Root ZFC CSLA. This design also achieves the performance of area as 22.129% and the performance of power as 26.210% when contrasted with CSLALOT. Along these lines CSLA utilizing ZFCLOT is distinguished plan that is more suitable for less force, area productive processors of DSP. Subsequently in the planned design, region and power enhancements are done which builds delay which is the significant constraint for this design.

#### REFERENCES

V. Siva Nagaraju, Rapaka Anusha, and Rajeev Ratna Vallabhuni, "A Hybrid PAPR Reduction Technique in OFDM Systems," 2020 IEEE International Women in Engineering

(WIE) Conference on Electrical and Computer Engineering (WIECON-ECE), Bhubaneswar, India, 26-27 Dec. 2020, pp. 364-367.

- [2] V. Siva Nagaraju, P. Ashok babu, B. Sadgurbabu, and Rajeev Ratna Vallabhuni, "Design and Implementation of Low power FinFET based Compressor," 2021 3rd International Conference on Signal Processing and Communication (ICP-SC), Coimbatore, India, 13-14 May 2021, pp. 532-536.

- [3] Rajeev Ratna Vallabhuni, J. Sravana, M. Saikumar, M. Sai Sriharsha, and D. Roja Rani, "An advanced computing architecture for binary to thermometer decoder using 18nm FinFET," 2020 Third International Conference on Smart Systems and Inventive Technology (ICSSIT), Tirunelveli, India, 20-22 August, 2020, pp. 510-515.

- [4] Rajeev Ratna Vallabhuni, K.C. Koteswaramma, B. Sadgurbabu, and Gowthamireddy A, "Comparative Validation of SRAM Cells Designed using 18nm FinFET for Memory Storing Applications," Proceedings of the 2nd International Conference on IoT, Social, Mobile, Analytics & Cloud in Computational Vision & Bio-Engineering (ISMAC-CVB 2020), 2020, pp. 1-10.

- [5] Rajeev Ratna Vallabhuni, Jujavarapu Sravana, Chandra Shaker Pittala, Mikkili Divya, B.M.S.Rani, and Vallabhuni Vijcaay, "Universal Shift Register Designed at Low Supply Voltages in 20nm FinFET Using Multiplexer," In Intelligent Sustainable Systems, pp. 203-212. Springer, Singapore, 2022.

- [6] P. Chandra Shaker, V. Parameswaran, M. Srikanth, V. Vijay, V. Siva Nagaraju, S.C. Venkateswarlu, Sadulla Shaik, and Vallabhuni Rajeev Ratna, "Realization and Comparative analysis of Thermometer code based 4-Bit Encoder using 18nm FinFET Technology for Analog to Digital Converters," In: Reddy V.S., Prasad V.K., Wang J., Reddy K.T.V. (eds) Soft Computing and Signal Processing. Advances in Intelligent Systems and Computing, vol 1325. Springer, Singapore. https://doi.org/10.1007/978-981-33-6912-2\_50

- [7] Rajeev Ratna Vallabhuni, G. Yamini, T. Vinitha, and S. Sanath Reddy, "Performance analysis: D-Latch modules designed using 18nm FinFET Technology," 2020 International Conference on Smart Electronics and Communication (ICOSEC), Tholurpatti, India, 10-12, September 2020, pp. 1171-1176.

- [8] Rani, B.M.S, Divyasree Mikkili, Rajeev Ratna Vallabhuni, Chandra Shaker Pittala, Vijay Vallabhuni, Suneetha Bobbillapati, and Bhavani Naga Prasanna, H., "Retinal Vascular Disease Detection from Retinal Fundus Images Using

Machine Learning," Australian Patent AU 2020101450. 12 Aug. 2020.

- [9] Rajeev Ratna Vallabhuni, D.V.L. Sravya, M. Sree Shalini, and G. Uma Maheshwararao, "Design of Comparator using 18nm FinFET Technology for Analog to Digital Converters," 2020 7th International Conference on Smart Structures and Systems (ICSSS), Chennai, India, 23-24 july, 2020, pp. 318-323.

- [10] Vallabhuni Rajeev Ratna, M. Saritha, Saipreethi. N, V. Vijay, P. Chandra Shaker, M. Divya, and Shaik Sadulla, "High Speed Energy Efficient Multiplier Using 20nm FinFET Technology," Proceedings of the International Conference on IoT Based Control Networks and Intelligent Systems (ICIC-NIS 2020), Palai, India, December 10-11, 2020, pp. 434-443. Available at SSRN: https://ssrn.com/abstract=3769235 or http://dx.doi.org/10.2139/ssrn.3769235

- [11] Rajeev Ratna Vallabhuni, S. Lakshmanachari, G. Avanthi, and Vallabhuni Vijay, "Smart Cart Shopping System with an RFID Interface for Human Assistance," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), Thoothukudi, India, 2020, pp. 165-169, doi: 10.1109/ICISS49785.2020.9316102.

- [12] Saritha, M., Kancharapu Chaitanya, Vallabhuni Vijay, Adam Aishwarya, Hasmitha Yadav, and G. Durga Prasad, "Adaptive And Recursive Vedic Karatsuba Multiplier Using Non Linear Carry Select Adder," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 22-29.

- [13] Vijay, Vallabhuni, Kancharapu Chaitanya, Chandra Shaker Pittala, S. Susri Susmitha, J. Tanusha, S. China Venkateshwarlu, and Rajeev Ratna Vallabhuni, "Physically Unclonable Functions Using Two-Level Finite State Machine," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 33-41.

- [14] Vijay, Vallabhuni, M. Sreevani, E. Mani Rekha, K. Moses, Chandra S. Pittala, KA Sadulla Shaik, C. Koteshwaramma, R. Jashwanth Sai, and Rajeev R. Vallabhuni, "A Review On N-Bit Ripple-Carry Adder, Carry-Select Adder And Carry-Skip Adder," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 27-32.

- [15] Vijay, Vallabhuni, Chandra S. Pittala, A. Usha Rani, Sadulla Shaik, M. V. Saranya, B. Vinod Kumar, RES Praveen Kumar, and Rajeev R. Vallabhuni, "Implementation of Fundamental Modules Using Quantum Dot Cellular Automata," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 12-19.

- [16] Vijay, Vallabhuni, Chandra S. Pittala, K. C. Koteshwaramma, A. Sadulla Shaik, Kancharapu Chaitanya, Shiva G. Birru, Soma R. Medapalli, and Varun R. Thoranala, "Design of Unbalanced Ternary Logic Gates and Arithmetic Circuits," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 20-26.

- [17] Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, Vallabhuni Vijay, Usha Rani Anam, Kancharapu Chaitanya, "Numerical analysis of various plasmonic MIM/MDM slot waveguide structures," International Journal of System Assurance Engineering and Management, 2022.

- [18] M. Saritha, M. Lavanya, G. Ajitha, Mulinti Narendra Reddy, P. Annapurna, M. Sreevani, S. Swathi, S. Sushma, Vallabhuni Vijay, "A VLSI design of clock gated technique based ADC lock-in amplifier," International Journal of System

Assurance Engineering and Management, 2022, pp. 1-8. https://doi.org/10.1007/s13198-022-01747-6.

- [19] Chandra Shaker Pittala, Vallabhuni Vijay, B. Naresh Kumar Reddy, "1-Bit FinFET Carry Cells for Low Voltage High-Speed Digital Signal Processing Applications," Silicon, 2022. https://doi.org/10.1007/s12633-022-02016-8.

- [20] Vallabhuni Vijay, Kancharapu Chaitanya, T. Sai Jaideep, D. Radha Krishna Koushik, B. Sai Venumadhav, Rajeev Ratna Vallabhuni, "Design of Optimum Multiplexer In Quantum-Dot Cellular Automata," International Conference on Innovative Computing, Intelligent Communication and Smart Electrical systems (ICSES -2021), Chennai, India, September 24-25, 2021.

- [21] S. China Venkateswarlu, N. Uday Kumar, D. Veeraswamy, and Vallabhuni Vijay, "Speech Intelligibility Quality in Telugu Speech Patterns Using a Wavelet-Based Hybrid Threshold Transform Method," International Conference on Intelligent Systems & Sustainable Computing (ICISSC 2021), Hyderabad, India, September 24-25, 2021.

- [22] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Low power based optimal design for FPGA implemented VMFU with equipped SPST technique," National Conference on Emerging Trends in Engineering Application (NCE-TEA-2011), India, June 18, 2011, pp. 224-227.

- [23] S. China Venkateswarlu, Ch. Sashi Kiran, R.V. Santhosh Nayan, Vijay Vallabhuni, P. Ashok Babu, V. Siva Nagaraju, "Artificial Intelligence Based Smart Home Automation System Using Internet of Things," The Patent Office Journal No. 09/2021, India. Application No. 202041057023 A.

- [24] Bandi Mary Sowbhagya Rani, Vasumathi Devi Majety, Chandra Shaker Pittala, Vallabhuni Vijay, Kanumalli Satya Sandeep, Siripuri Kiran, "Road Identification Through Efficient Edge Segmentation Based on Morphological Operations," Traitement du Signal, vol. 38, no. 5, Oct. 2021, pp. 1503-1508.

- [25] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Optimal design of VLSI implemented Viterbi decoding," National conference on Recent Advances in Communications & Energy Systems, (RACES-2011), Vadlamudi, India, December 5, 2011, pp. 67-71.

- [26] Katikala Hima Bindu, Sadulla Shaik, V. Vijay, "FINFET Technology in Biomedical-Cochlear Implant Application," International Web Conference on Innovations in Communication and Computing, ICICC '20, India, October 5, 2020.

- [27] V. Vijay, J. Prathiba, S. Niranjan Reddy, V. Raghavendra Rao, "Energy efficient CMOS Full-Adder Designed with TSMC 0.18µm Technology," International Conference on Technology and Management (ICTM-2011), Hyderabad, India, June 8-10, 2011, pp. 356-361.

- [28] Vallabhuni Vijay, Pittala Chandra shekar, Shaik Sadulla, Putta Manoja, Rallabhandy Abhinaya, Merugu rachana, and Nakka nikhil, "Design and performance evaluation of energy efficient 8-bit ALU at ultra low supply voltages using FinFET with 20nm Technology," VLSI Architecture for Signal, Speech, and Image Processing, edited by Durgesh Nandan, Basant Kumar Mohanty, Sanjeev Kumar, Rajeev Kumar Arya, CRC press, 2021.

- [29] P. Ashok Babu, V. Siva Nagaraju, and Rajeev Ratna Vallabhuni, "Speech Emotion Recognition System With Librosa," 2021 10th IEEE International Conference on Communi-

cation Systems and Network Technologies (CSNT), Bhopal, India, 18-19 June 2021, pp. 421-424.

- [30] P. Ashok Babu, V. Siva Nagaraju, and Rajeev Ratna Vallabhuni, "8-Bit Carry Look Ahead Adder Using MGDI Technique," IoT and Analytics for Sensor Networks, Springer, Singapore, 2022, pp. 243-253.

- [31] Dr. S. Selvakanmani, Mr. Rajeev Ratna Vallabhuni, Ms. B. Usha Rani, Ms. A. Praneetha, Dr. Urlam Devee Prasan, Dr. Gali Nageswara Rao, Ms. Keerthika. K, Dr. Tarun Kumar, Dr. R. Senthil Kumaran, Mr. Prabakaran.D, "A Novel Global Secure Management System with Smart Card for IoT and Cloud Computing," The Patent Office Journal No. 06/2021, India. International classification: H04L29/08. Application No. 202141000635 A.

- [32] Nalajala Lakshman Pratap, Rajeev Ratna Vallabhuni, K. Ramesh Babu, K. Sravani, Bhagyanagar Krishna Kumar, Angothu Srikanth, Pijush Dutta, Swarajya Lakshmi V Papineni, Nupur Biswas, K.V.S.N.Sai Krishna Mohan, "A Novel Method of Effective Sentiment Analysis System by Improved Relevance Vector Machine," Australian Patent AU 2020104414. 31 Dec. 2020

- [33] S.V.S Prasad, Chandra Shaker Pittala, V. Vijay, and Rajeev Ratna Vallabhuni, "Complex Filter Design for Bluetooth Receiver Application," In 2021 6th International Conference on Communication and Electronics Systems (ICCES), Coimbatore, India, July 8-10, 2021, pp. 442-446.

- [34] Chandra Shaker Pittala, J. Sravana, G. Ajitha, P. Saritha, Mohammad Khadir, V. Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Novel Methodology to Validate DUTs Using Single Access Structure," 5th International Conference on Electronics, Materials Engineering and Nano-Technology (IEMENTech 2021), Kolkata, India, September 24-25, 2021, pp. 1-5.

- [35] Chandra Shaker Pittala, M. Lavanya, V. Vijay, Y.V.J.C. Reddy, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Energy Efficient Decoder Circuit Using Source Biasing Technique in CNTFET Technology," 2021 Devices for Integrated Circuit (DevIC), Kalyani, India, May 19-20, 2021, pp. 610-615.

- [36] Chandra Shaker Pittala, M. Lavanya, M. Saritha, V. Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Biasing Techniques: Validation of 3 to 8 Decoder Modules Using 18nm FinFET Nodes," 2021 2nd International Conference

for Emerging Technology (INCET), Belagavi, India, May 21-23, 2021, pp. 1-4.

- [37] P. Ashok Babu, V. Siva Nagaraju, Ramya Mariserla, and Rajeev Ratna Vallabhuni, "Realization of 8 x 4 Barrel shifter with 4-bit binary to Gray converter using FinFET for Low Power Digital Applications," Journal of Physics: Conference Series, vol. 1714, no. 1, p. 012028. IOP Publishing. doi:10.1088/1742-6596/1714/1/012028

- [38] Vallabhuni Vijay, C. V. Sai Kumar Reddy, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, M. Saritha, M. Lavanya, S. China Venkateswarlu and M. Sreevani, "ECG Performance Validation Using Operational Transconductance Amplifier with Bias Current," International Journal of System Assurance Engineering and Management, vol. 12, iss. 6, 2021, pp. 1173-1179.

- [39] Vallabhuni, Rajeev Ratna, M. Saritha, Sruthi Chikkapally, Vallabhuni Vijay, Chandra Shaker Pittala, and Sadulla Shaik, "Universal Shift Register Designed at Low Supply Voltages in 15 nm CNTFET Using Multiplexer," In International Conference on Emerging Applications of Information Technology, pp. 597-605. Springer, Singapore, 2021.

- [40] B. M. S. Rani, Vallabhuni Rajeev Ratna, V. Prasanna Srinivasan, S. Thenmalar, and R. Kanimozhi, "Disease prediction based retinal segmentation using bi-directional ConvLSTMU-Net," Journal of Ambient Intelligence and Humanized Computing, 2021, pp. 1-10. https://doi. org/10.1007/s12652-021-03017-y

- [41] Rajeev Ratna Vallabhuni, A. Karthik, CH. V. Sai Kumar, B. Varun, P. Veerendra, and Srisailam Nayak, "Comparative Analysis of 8-Bit Manchester Carry Chain Adder Using FinFET at 18nm Technology," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), Thoothukudi, India, 2020, pp. 1579-1583, doi: 10.1109/ ICISS49785.2020.9316061.

- [42] R. R. Vallabhuni, P. Shruthi, G. Kavya and S. Siri Chandana, "6Transistor SRAM Cell designed using 18nm FinFET Technology," 2020 3rd International Conference on Intelligent Sustainable Systems (ICISS), Thoothukudi, India, 2020, pp. 1584-1589, doi: 10.1109/ICISS49785.2020.9315929.

- [43] Vallabhuni Vijay, and Avireni Srinivasulu, "A Novel Square Wave Generator Using Second Generation Differential Current Conveyor," Arabian Journal for Science and Engineering, vol. 42, iss. 12, 2017, pp. 4983-4990.