### **RESEARCH ARTICLE**

# Ultra Low Potential Operated Fundamental Arithmetic Module Design for High-Throughput Applications

O.J.M. Smith<sup>1</sup>, F. de Mendonça<sup>2</sup>, K.N. Kantor<sup>3</sup>, A. A. Zaky<sup>4</sup>, G.F. Freire<sup>5</sup>

<sup>1-5</sup>Departamento de Engenharia Elétrica, Universidade Federal de Pernambuco - UFPE Recife, Brazil

#### **KEYWORDS:**

Delay, FinFET, Logic Gates, Multiplier,

Power...

#### ARTICLE HISTORY:

Received 18.07.2022 Accepted 24.08.2022 Published 28.09.2022

#### DOI:

https://doi.org/10.31838/jvcs/04.01.08

#### **A**BSTRACT

The multiplier is an electronic circuit used in digital electronics [1], to multiply two binary numbers. The advantages of the multiplier are low power consumption, regularity of layout, less chip area, high speed etc. Multiplier plays an important role in today's digital processing and various applications. Multipliers are the key components in some high speed systems such as FIR filters, microprocessors, ALU and other commercial applications like computers, mobiles, high speed calculators and some general-purpose processors require binary multipliers. Since last few years, the tiny size of MOSFET, that is less than tens of nanometers, created some operational problems such as increased gate-oxide leakage, amplified junction leakage, high sub threshold conduction and reduced output resistance. To overcome the above problems, FinFET has the advantages of an increase in the operating speed, reduced power consumption, reduced static leakage current is used to realize the majority of the applications by replacing MOSFET. By considering the attractive features of the FinFET, a multiplier is designed as an application. Sequential circuits are extensively used in the design of memory elements such as flip flops and register. Registers are used as data storage devices in low power VLSI designs. The design is simulated using Cadence virtuoso with 20nm technology. Comparative performance analysis is carried out in contrast to the other standard circuits by taking the important performance metrics such as delay, power and power delay product (PDP), energy delay product (EDP) metrics into consideration.

**Author's e-mail:** smith.ojm@cesmac.edu.br, f.de.mend@cesmac.edu.br, kantor.kn@cesmac.edu.br, fg.freire@cesmac.edu.br

How to cite this article: Smith OJM, de Mendonça F, Kantor KN, Zaky AA, Freire GF. Ultra Low Potential Operated Fundamental Arithmetic Module Design for High-Throughput Applications. Journal of Complementary Research, Vol. 4, No. 1, 2022 (pp. 52-59).

## Introduction

The multiplier is an electronic circuit used in digital electronics such a computer,<sup>[1]</sup> to multiply two binary numbers. Compared to addition and subtraction, multiplication is a complex process.<sup>[2]</sup> Various computer arithmetic techniques can be used to implement a digital multiplier.<sup>[3]</sup> Most techniques involve computing a set of partial products, and then summing the partial product together. The binary multiplication follows the same process for producing the product results of the two binary numbers. The binary multiplication is easier as it contains only 0's and 1's.<sup>[2-16]</sup>

The advantages of the multiplier are low power consumption, regularity of layout, less chip area, high speed etc. Multiplier plays an important role in today's digital processing and various applications. [4] The multiplier is also used in commercial applications like computers, mobiles, high speed calculators and some general-purpose processors require binary multipliers. [17-25]

As the technology advances day-by-day power consumption in battery-operated transportable devices creates a serious concern. MOSFET is widely used now days. Below 45nm technology, controlling the channel of the MOSFET becomes difficult.<sup>[5]</sup> The other drawbacks of MOSFET implementation are that the power consumption

is high; the delay is also high and large amount of current leaks through the body of the circuit. It also creates operational problems such as gate-oxide leakage, amplified junction leakage, high sub threshold conduction and reduced output resistance.<sup>[26]</sup>

The FinFET has overcome all the drawbacks of the MOSFET to a great extent. The multiplier using FinFET is designed at 20 nm technology which reduces the silicon area. Using the FinFET the power consumption is reduced and the overall delay of the circuit is also reduced. The operational speed of the circuit is also increased compared to the circuit designed using MOSFET. The operational problems faced by using MOSFET are overthrown by replacing MOSFET with FinFET, the output resistance is increased and the leakages caused by MOSFET which includes gate-oxide leakage and the amplified junction leakage are blown-away.<sup>[27-34]</sup>

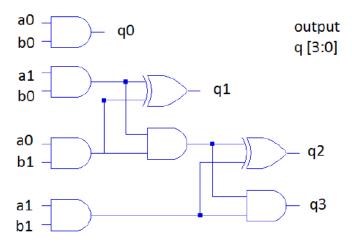

The 2x2 multiplier has two inputs A and B each of 2bit size namely A0, A1 and B0, B1 and it has four outputs Y0, Y1, Y2, and Y3. The circuit designed using MOSFET consists of the following components, they include six AND gates and two EXOR gates. First, the multiplier circuit is implemented using MOSFET in cadence virtuoso tool. The power and the overall delay of the circuit implemented using MOSFET is calculated. The code for the circuit in FinFET using 20nm technology is written, first the program for the individual gates is developed i.e., the code for the AND gate and the EXOR gate are developed, after developing the code for the individual gates then these two programs are combined to develop the code for the entire multiplier circuit and executed using cadence virtuoso tool to get the desired results, the power and the overall delay of the circuit is calculated. Finally results of both the techniques are compared.[35-39]

This manuscript has six sections. The first section is all about the introduction to the existing method, proposed method and the advancements made in the circuit. The second section elaborates the brief information about the FinFET characteristics and modeling. In the third section the entire details of the proposed circuit design and realization of the proposed circuit are discussed. The details about the simulation results of proposed design are presented in the fourth section. Finally, the fifth section consists of the conclusion part of the proposed circuit. The references are attached at the end of the paper.

## FINFET CHARACTERISTICS AND MODELING

A Fin Field-effect transistor (FinFET) is a MOSFET built on a substrate where the gate is placed on two, three, or four sides of the channel or wrapped around the channel, forming a double gate structure. These devices have been given the generic name "FinFET" because the source/drain region forms fins on the silicon surface. The body of the

FinFET is very thin, around 10nm or less. So, there is no leakage path which effectively controls the leakage. The channel is double-gate structure. The drive current of the FinFET can be increased by increasing the width of the channel i.e. by increasing the height of the fin. We can also increase the device drive current by constructing parallel multiple fins connected together. It implies that for a FinFET, the arbitrary channel width is not possible, since it is always a multiple of fin height. So, effective width of the device becomes quantized. While in planner devices, there is the freedom to choose the device's drive strength by varying channel width. It implies that FinFET suffers less from dopant induced variations. Low channel doping also ensures better mobility of the carrier inside the channel.

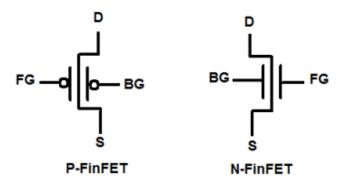

The basic structure of FinFET is that the conducting channel is wrapped by a thin Silicon fin. This forms the body of the device. The fins are the 3D channel between the source and the drain terminals. They are built on top if silicon (Si) substrate. The gate terminal is wrapped around the channel .The below figure 1 represents the symbolic notation of the FinFET. The "fin" refers to the narrow channel between source and drain. A thin insulating oxide layer on either side of the fin separates it from the gate. FinFET with a thick oxide on top of the fin are called double-gate and those with a thin oxide on top as well as on the sides are called triple-gate FinFET [9]. The figure 2 represents the symbol of the N type FinFET and also P type FinFET.

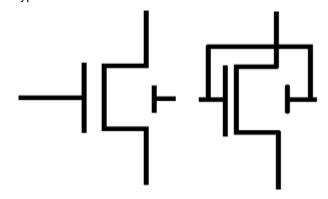

Fg. 1: Symbolic Notation of FinFET

Fig. 2: Symbols of FinFET

The FinFET has better Sub threshold swing than the MOSFET. The control of short channel effect is better in FinFET compared to MOSFET. The FinFET exhibits negligible body effect and also it has very little static leakage. It exhibits high output resistance and high sub threshold conduction.

The advantages of the FinFET are low power consumption, it occupies less chip area and it exhibits high operational speed. It exhibits little or sometimes no body effect and the delay of the circuit is also reduced and the FinFET devices have significantly faster switching times and higher current density than the mainstream MOSFET technology. [10] The FinFET is used only below 45nm technology. It is effectively used to design many combinational and sequential circuits in order to improve their performance characteristics. [11]

## PROPOSED CIRCUIT: DESIGN AND REALIZATION

The FinFET has overcome all the drawbacks of the MOSFET to a great extent. The multiplier using FinFET is designed at 20 nm technology which reduces the silicon area. The design is simulated using cadence virtuoso with 20nm technology. Using the FinFET the power consumption is reduced and the overall delay of the circuit is also reduced. The operational speed of the circuit is also increased compared to the circuit designed using MOSFET. The static leakage current is also reduced when compared to that of the MOSFET implementation.

#### **Circuit Diagram**

The Fig 3 is the circuit diagram of the 2x2 multiplier. The multiplier has inputs each of 2bits namely a0, a1 and b0, b1 and 4 outputs q0, q1, q2, q3. The multiplier circuit consists of 6 AND gates and 2 EXOR gates.

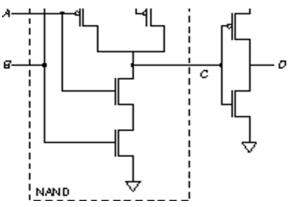

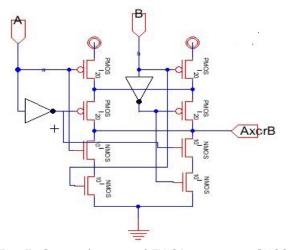

The Fig 4 represents the circuit diagram of the AND gate. The AND gate is designed using CMOS. The AND gate has inputs namely A and B and output O. In the circuit the

Fig. 3: Circuit diagram of 2x2Multiplier

NAND gate output is connected to the inverter in order to produce the AND gate output. The AND gate Boolean expression is A.B.

The Fig 5 is the circuit diagram of the EXOR gate. The EXOR gate is designed using CMOS. The EXOR gate has inputs namely A and B and output Y. The EXOR gate Boolean expression is  $A\oplus B$  .

**Truth Table**Truth table of 2x2Multiplier

| AO     A1     BO     B1     YO     Y1     Y2     Y3       0     0     0     0     0     0     0     0     0       0     0     0     0     0     0     0     0     0       0     0     1     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0 |    |    |    |    |    |    |    |    |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|----|--|

| 0   0   0   1   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0                                                                                                                                                                 | A0 | A1 | ВО | B1 | Y0 | Y1 | Y2 | Y3 |  |

| 0   0   1   0   0   0   0   0   0     0   0   1   1   0   0   0   0   0     0   1   0   0   0   0   0   1   0     0   1   1   0   0   0   1   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0 </td <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td></td>                                                                | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| 0   0   1   1   0   0   0   0   0     0   1   0   0   0   0   0   0   0     0   1   0   1   0   0   0   1   0     0   1   1   0   0   0   0   1   1     1   0   0   0   0   0   0   0   0     1   0   1   0   0   1   0   0   0     1   0   1   0   0   0   0   0   0     1   0   1   1   0   0   0   0   0     1   1   0   0   0   0   0   0   0     1   1   0   1   0   0   0   0   0     1   1   0   1   0   0   0   0   0     1   1   0   1   0   0   1   1 <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td></td>                                                                                         | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |  |

| 0   1   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   1   0   0   1   0   0   1   0   0   1   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0                                                                                                                                                                 | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |  |

| 0   1   0   1   0   0   0   1     0   1   1   0   0   0   1   0     0   1   1   0   0   0   1   0     1   0   0   0   0   0   0   0     1   0   1   0   0   1   0   0     1   0   1   0   0   0   0   0     1   0   1   0   0   0   0   0     1   1   0   1   0   0   0   0     1   1   0   1   0   0   0   0     1   1   0   1   0   0   1   1     1   1   0   0   0   0   0   0     1   1   0   0   0   1   1   0     1   1   0   0   0   1   1   0                                                                                                                                                                                                     | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  |  |

| 0   1   1   0   0   0   1   0     0   1   1   1   0   0   1   1     1   0   0   0   0   0   0   0     1   0   0   1   0   0   1   0   0     1   0   1   1   0   0   0   0   0   0     1   1   0   1   0   0   0   0   0   0     1   1   0   1   0   0   1   1   0     1   1   0   0   0   0   0   0   0     1   1   0   0   0   1   1   0     1   1   0   0   0   1   1   0                                                                                                                                                                                                                                                                               | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| 0   1   1   1   0   0   1   1     1   0   0   0   0   0   0   0     1   0   0   1   0   0   1   0   0     1   0   1   0   0   1   0   0   0   0     1   1   0   0   0   0   0   0   0   0   0     1   1   0   1   0   0   1   1   1   0   1   1   0     1   1   1   0   0   1   1   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   <                                                                                                                                                                             | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 1  |  |

| 1   0   0   0   0   0   0   0     1   0   0   1   0   0   1   0     1   0   1   0   0   1   0   0     1   0   1   1   0   0   0   0   0     1   1   0   1   0   0   0   0   0   0     1   1   0   1   0   0   1   1   0     1   1   1   0   0   1   1   0                                                                                                                                                                                                                                                                                                                                                                                                 | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 0  |  |

| 1   0   0   1   0   0   1   0     1   0   1   0   0   1   0   0     1   0   1   1   0   0   0   0   0     1   1   0   1   0   0   0   0   0   0     1   1   0   1   0   0   1   1   0   0   0   1   1   0                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 1  |  |

| 1 0 1 0 0 1 0 0   1 0 1 1 0 1 1 0   1 1 0 0 0 0 0 0   1 1 0 1 0 0 1 1   1 1 1 0 0 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| 1 0 1 1 0 1 1 0   1 1 0 0 0 0 0 0   1 1 0 1 0 0 0 1 1   1 1 1 0 0 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  |  |

| 1 1 0 0 0 0 0 0   1 1 0 1 0 0 1 1   1 1 1 0 0 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  |  |

| 1 1 0 1 0 0 1 1<br>1 1 0 0 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 0  |  |

| 1 1 1 0 0 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1  | 1  | 0  | 1  | 0  | 0  | 1  | 1  |  |

| 1 1 1 1 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  | 1  | 1  | 0  | 0  | 1  | 1  | 0  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 1  |  |

Truth table of AND gate

| Input A | Input B | Y = AB |

|---------|---------|--------|

| 0       | 0       | 0      |

| 0       | 1       | 0      |

| 1       | 0       | 0      |

| 1       | 1       | 1      |

Fig. 4: Circuit diagram of AND gate using CMOS

The basic multiplication algorithm recursively applies the following multiply step to each successive bit of the multiplier beginning with its LSB. AND the multiplier bit with the entire multiplicand, add the result to the accumulating partial product, and shift the accumulating partial product and multiplier one bit to the right. Repeat this step until the MSB of the multiplier has been processed, and read the final product.[12] Consider the multiplication of two 4-bit numbers, as shown in Figure 2. The multiplicand is A1, A0 the multiplier is B1, B0 and the product is y3, y2, y1 and y0. The first partial product is formed by multiplying A1, A0 by B0. The multiplication of two bits such as A0 and B0 produces y0 as 1 if both bits are 1; otherwise it produces 0 as output. This is identical to an AND operation. Therefore, the partial product can be implemented with AND gates as shown in the figure 2. The second partial y1 product is formed by multiplying A0, B1 and is shifted one position to the left. The sum of the two partial products is produced by a binary adder. Note that the least significant bit of the product does not have to go through an adder, since it is completely formed by the output of the first AND gate. The same approach as used for multiplier bit y1 is also used for multiplier bits y2 and y3. Note that the carry out can be 1, so it enters the MSB of the adder at the next level down. In general, for J multiplier bits and K multiplicand bits, we need  $(J \times K)$ AND gates and (J-1) K-bit adders to produce a product

Fig. 5: Circuit diagram of EX-OR gate using CMOS

#### Truth table of EX-OR gate

| Inputs |   | Outputs          |

|--------|---|------------------|

| X      | Υ | $Y = A \oplus B$ |

| 0      | 0 | 0                |

| 0      | 1 | 1                |

| 1      | 0 | 1                |

| 1      | 1 | 0                |

of J+K bits. For the Example multiplier, K=2 and J=2, so we need 4 AND gates and one 2-bit adder to produce a product of 4 bits.<sup>[13]</sup>

# **Simulation Results of Proposed Method**

## **Transient Response**

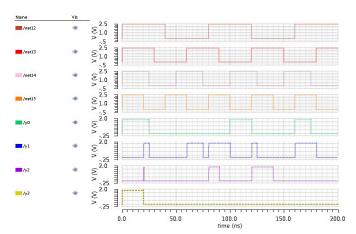

The Fig 6 is the transient response of the multiplier using MOSFET. In the above graph there are 4 inputs namely net2, net3, net4, net5 and there are 4 outputs namely y0, y1, y2, y3. As the input is varied as shown in the graph corresponding output is produced.

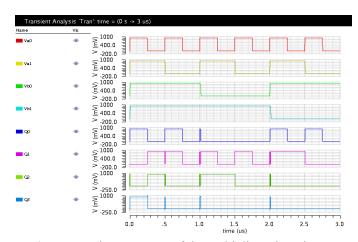

The Fig 7 gives the transient response of the multiplier using FinFET. In the above graph there are 4 inputs namely Va0, Va1, Vb0, Vb1 and 4 outputs namely Q0, Q1, Q2, Q3. As the input is varies with time as shown in the graph corresponding output is produced.

## **Vdd Vs Delay**

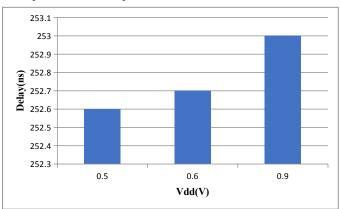

The Fig 8 is the graph plotted between Vdd and delay of the multiplier. The output produced by varying the voltage between 0V to 1V is plotted in the above fig 8; the output corresponds to the output of the multiplier realized using FinFET.

Fig. 6: Transient response of multiplier using MOSFET

Fig. 7: Transient response of the multiplier using FinFET

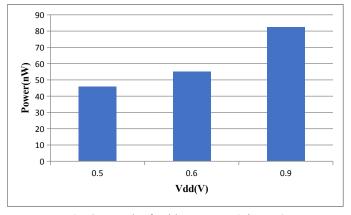

#### **Vdd Vs Power**

The Fig 9 is the graph which gives the information regarding the power of the multiplier with respect to the voltage variations between 0V to 1V. The graph plotted between Vdd and Power of the multiplier realized using FinFET.

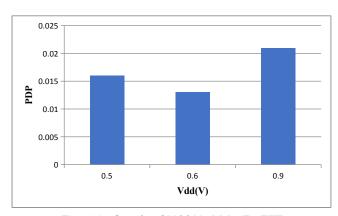

## **Vdd Vs PDP**

The information of the PDP (power delay product) values of the multiplier is plotted in Fig 10. The graph is all about the graph plotted between voltage and the PDP of multiplier realized using FinFET.

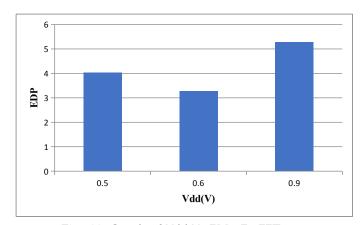

#### **Vdd Vs EDP**

The Fig 11 is the graph plotted between Vdd Vs EDP (Energy delay product) of the multiplier realized using FinFET. The corresponding EDP (energy delay product) values increases with the increase in the voltage of the multiplier.

## **Comparative Analysis**

Fig. 8: Graph of Vdd Vs Delay (FinFET)

Fig. 9: Graph of Vdd Vs Power (FinFET)

The multiplier circuit using FinFET consumes low power and the overall delay of the circuit is minimized to great extent compared to that of the multiplier using MOSFET. Using FinFET very little current is leaked from the body of the circuit. The chip area is minimized and the wafer cost is also cheaper. The operational speed of the circuit is also high.

Multiplier is mainly used in the digital signal processing applications and various applications such as computers and high speed calculators, majorly used in mobiles and general purpose processors, true RMS converter and ring modulator. It is a key component of many high performance systems such as FIR filters, Microprocessors, ALU etc.<sup>[14]</sup> It is also incorporated into many applications, such as variablegain amplifier, product detector, frequency mixers. It is effectively used in the companding technique and PAM and automatic gain control.<sup>[15]</sup>

Fig. 10: Graph of Vdd Vs PDP (FinFET).

Fig. 11: Graph of Vdd Vs EDP (FinFET).

| Vdd(V) | Power    |          | L       | Delay    |         | PDP      |          | EDP        |  |

|--------|----------|----------|---------|----------|---------|----------|----------|------------|--|

|        | LVt      | Normal   | LVt     | Normal   | LVt     | Normal   | LVt      | Normal     |  |

| 0.1    | 1.74 kW  | 2.077 uW | 7.03 us | 16.81 ns | 12.23 k | 0.03 p   | 85.97 k  | 0.000504 a |  |

| 0.5    | 41.57 mW | 2.497 uW | 5.86 ns | 3.751 ns | 24.36 n | 0.009 p  | 0.0142 f | 0.000036 a |  |

| 0.6    | 49.89 mW | 2.998 uW | 5.799ns | 3.506 ns | 28.93 n | 0.0105 p | 0.0167 f | 0.000033 a |  |

## **CONCLUSION**

This project implements the optimized low power and high speed FinFET based Multiplier using 20nm technology which is simulated using cadence virtuoso tool. Power performance is improved and delay is improved to great extent. Here comparative analysis of MOSFET and FinFET based Multiplier is also done which shows that FinFET based multiplier at 20nm technology is better than MOSFET based multiplier in terms of power, delay, power delay product(PDP) and energy delay product(EDP). The proposed circuit has some limitations that is the proposed multiplier circuit does not respond for the voltages as given they are 0.2V, 0.3V, 0.4V, 0.6V, 0.7V, 0.9V and 1V. The circuit also limitations like the proposed circuit does not respond for the HVt (high threshold) voltages between 0.1V to 1V.

### REFERENCES

- [1] Chen. Y, Dinavahi V. Hardware emulation building blocks of real-time simulation of large-scale power grids. IEEE Transactions on Industrial Information. 2014 Feb;10(1):373-81.

- [2] Vallabhuni Vijay, V.R. Seshagiri Rao, Kancharapu Chaitanya, S. China Venkateshwarlu, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, "High-Performance IIR Filter Implementation Using FPGA," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [3] Jujavarapu Sravana, S.K. Hima Bindhu, K. Sharvani, P. Sai Preethi, Saptarshi Sanyal, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "Implementation of Spurious Power Suppression based Radix-4 Booth Multiplier using Parallel Prefix Adders," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-6.

- [4] Chandra Shaker Pittala, Vallabhuni Vijay, A. Usha Rani, R. Kameshwari, A. Manjula, D.Haritha, Rajeev Ratna Vallabhuni, "Design Structures Using Cell Interaction Based XOR in Quantum Dot Cellular Automata," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [5] S. China Venkateshwarlu, Mohammad khadir, V. Vijay, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, "Optimized Design of Power Efficient FIR Filter Using Modified Booth Multiplier," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [6] G. Naveen, V.R Seshagiri Rao, Nirmala. N, Pavan kalyan. L, Vallabhuni Vijay, S. China Venkateswarlu, Rajeev Ratna Vallabhuni, "Design of High-Performance Full Adder Using 20nm CNTFET Technology," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [7] Mohammad khadir, S. Shakthi, S. Lakshmanachari, Vallabhuni Vijay, S. China Venkateswarlu, P. Saritha, Rajeev

- Ratna Vallabhuni, "QCA Based Optimized Arithmetic Models," 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST-2021), Jamshedpur, India, February 11-12, 2022, pp. 1-5.

- [8] P. Ashok Babu, P. Sridhar, and Rajeev Ratna Vallabhuni, "Fake Currency Recognition System Using Edge Detection," 2022 Interdisciplinary Research in Technology and Management (IRTM), Kolkata, India, February 24-26, 2022, pp. 1-5.

- [9] Koteshwaramma, K. C., Vallabhuni Vijay, V. Bindusree, Sri Indrani Kotamraju, Yasala Spandhana, B. Vasu D. Reddy, Ashala S. Charan, Chandra S. Pittala, and Rajeev R. Vallabhuni, "ASIC Implementation of An Effective Reversible R2B Fft for 5G Technology Using Reversible Logic," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 5-13.

- [10] Vijay, Vallabhuni, Kancharapu Chaitanya, Chandra Shaker Pittala, S. Susri Susmitha, J. Tanusha, S. China Venkateshwarlu, and Rajeev Ratna Vallabhuni, "Physically Unclonable Functions Using Two-Level Finite State Machine," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 33-41.

- [11] Vijay, Vallabhuni, M. Sreevani, E. Mani Rekha, K. Moses, Chandra S. Pittala, KA Sadulla Shaik, C. Koteshwaramma, R. Jashwanth Sai, and Rajeev R. Vallabhuni, "A Review On N-Bit Ripple-Carry Adder, Carry-Select Adder And Carry-Skip Adder," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 27-32.

- [12] Vijay, Vallabhuni, Chandra S. Pittala, A. Usha Rani, Sadulla Shaik, M. V. Saranya, B. Vinod Kumar, RES Praveen Kumar, and Rajeev R. Vallabhuni, "Implementation of Fundamental Modules Using Quantum Dot Cellular Automata," Journal of VLSI circuits and systems, vol. 4, no. 01, 2022, pp. 12-19.

- [13] Gollamandala Udaykiran Bhargava, Vasujadevi Midasala, and Vallabhuni Rajeev Ratna, "FPGA implementation of hybrid recursive reversable box filter-based fast adaptive bilateral filter for image denoising," Microprocessors and Microsystems, vol. 90, 2022, 104520.

- [14] Ratna, Vallabhuni Rajeev, and Ramya Mariserla. "Design and Implementation of Low Power 32-bit Comparator." (2021).

- [15] Vallabhuni Vijay, Kancharapu Chaitanya, T. Sai Jaideep, D. Radha Krishna Koushik, B. Sai Venumadhav, Rajeev Ratna Vallabhuni, "Design of Optimum Multiplexer In Quantum-Dot Cellular Automata," International Conference on Innovative Computing, Intelligent Communication and Smart Electrical systems (ICSES -2021), Chennai, India, September 24-25, 2021.

- [16] S. Sushma, S. Swathi, V. Bindusree, Sri Indrani Kotamraju, A. Ashish Kumar, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "QCA Based Universal Shift Register using 2 to 1 Mux and D flip-flop," IEEE 2021 International Conference on Advances in Computing, Communication and Control (ICAC3'21) 7th Edition (3rd and 4th December 2021), Mumbai, Maharashtra, India, December 03-04, 2021, pp. 1-6.

- [17] M. Sreevani, S. Lakshmanachari, B. Manvitha, Y.J.N. Pravalika, T.Praveen, V.Vijay, Rajeev Ratna Vallabhuni, "Design of Carry Select Adder Using Logic Optimization Technique," IEEE 2021 International Conference on Advances in Computing, Communication and Control (ICAC3'21) 7th

- Edition (3rd and 4th December 2021), Mumbai, Maharashtra, India, December 03-04, 2021, pp. 1-6.

- [18] M. Saritha, Chelle Radhika, M. Narendra Reddy, M. lavanya, A. Karthik, Vallabhuni Vijay, Rajeev Ratna Vallabhuni, "Pipelined Distributive Arithmetic-based FIR Filter Using Carry Save and Ripple Carry Adder," Second IEEE International Conference on Communication, Computing and Industry 4.0 (C2I4-2021), Bengaluru, Karnataka, India, December 16-17, 2021, pp. 1-6.

- [19] S. Swathi, S. Sushma, V. Bindusree, L Babitha, Sukesh Goud. K, S. Chinavenkateswarlu, V. Vijay, Rajeev Ratna Vallabhuni, "Implementation of An Energy-Efficient Binary Square Rooter Using Reversible Logic By Applying The Non-Restoring Algorithm," Second IEEE International Conference on Communication, Computing and Industry 4.0 (C2I4-2021), Bengaluru, Karnataka, India, December 16-17, 2021, pp. 1-6.

- [20] Kiran, K. Uday, Gowtham Mamidisetti, Chandra shaker Pittala, V. Vijay, and Rajeev Ratna Vallabhuni, "A PCCN-Based Centered Deep Learning Process for Segmentation of Spine and Heart: Image Deep Learning," In Handbook of Research on Technologies and Systems for E-Collaboration During Global Crises, pp. 15-26. IGI Global, 2022.

- [21] Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, Vallabhuni Vijay, Usha Rani Anam, Kancharapu Chaitanya, "Numerical analysis of various plasmonic MIM/MDM slot waveguide structures," International Journal of System Assurance Engineering and Management, 2022.

- [22] Chandra Shaker Pittala, Vallabhuni Vijay, B. Naresh Kumar Reddy, "1-Bit FinFET Carry Cells for Low Voltage High-Speed Digital Signal Processing Applications," Silicon, 2022. https://doi.org/10.1007/s12633-022-02016-8.

- [23] M. Saritha, M. Lavanya, G. Ajitha, Mulinti Narendra Reddy, P. Annapurna, M. Sreevani, S. Swathi, S. Sushma, Vallabhuni Vijay, "A VLSI design of clock gated technique based ADC lock-in amplifier," International Journal of System Assurance Engineering and Management, 2022, pp. 1-8. https://doi.org/10.1007/s13198-022-01747-6

- [24] B. M. S. Rani, Vallabhuni Rajeev Ratna, V. Prasanna Srinivasan, S. Thenmalar, and R. Kanimozhi, "Disease prediction based retinal segmentation using bi-directional ConvLSTMU-Net," Journal of Ambient Intelligence and Humanized Computing, 2021, pp. 1-10. <a href="https://doi.org/10.1007/s12652-021-03017-y">https://doi.org/10.1007/s12652-021-03017-y</a>

- [25] Vallabhuni Vijay, J. Sravana, K.S. Indrani, G. Ajitha, A. Prashanth, K. Nagaraja, K.C. Koteswaramma, C. Radhika, M. Hima Bindu, N. Manjula, "A SYSTEM FOR CONTROLLING POSITIONING ACCORDING TO MOVEMENT OF TERMINAL IN WIRELESS COMMUNICATION BASED ON AI INTERFACE," The Patent Office Journal No. 50/2021, India. Application No. 202141055995 A.

- [26] Dr. L.V. Narasimha Prasad, Dr. Vijay Vallabhuni, Dr. S. China Venkateswarlu, Dr. V. Vhandra Jagan Mohan, Ms. P. Sruthilaya, Mr. K. Tarun Kumar, Mr. B. Raju, Mr. P. Ravinder, "Garbage Collector with Smart Segregation and Method of Segregation Thereof," The Patent Office Journal No. 04/2022, India. Application No. 202141062270 A.

- [27] Sravana, J., K. S. Indrani, M. Saranya, P. Sai Kiran, C. Reshma, and Vallabhuni Vijay, "Realisation of Performance

- Optimised 32-Bit Vedic Multiplier," Journal of VLSI circuits and systems, vol. 4, no. 2, 2022, pp. 14-21.

- [28] V. Vijay, J. Prathiba, S. Niranjan Reddy, V. Raghavendra Rao, "Energy efficient CMOS Full-Adder Designed with TSMC 0.18μm Technology," International Conference on Technology and Management (ICTM-2011), Hyderabad, India, June 8-10, 2011, pp. 356-361.

- [29] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Optimal design of VLSI implemented Viterbi decoding," National conference on Recent Advances in Communications & Energy Systems, (RACES-2011), Vadlamudi, India, December 5, 2011, pp. 67-71.

- [30] Ch. Srivalli, S. Niranjan reddy, V. Vijay, J. Pratibha, "Low power based optimal design for FPGA implemented VMFU with equipped SPST technique," National Conference on Emerging Trends in Engineering Application (NCE-TEA-2011), India, June 18, 2011, pp. 224-227.

- [31] Vallabhuni Vijay, and Avireni Srinivasulu, "A Novel Square Wave Generator Using Second Generation Differential Current Conveyor," Arabian Journal for Science and Engineering, vol. 42, iss. 12, 2017, pp. 4983-4990.

- [32] L. Babitha, U. Somanaidu, CH. Poojitha, K. Niharika, V. Mahesh, and Vallabhuni Vijay, "An Efficient Implementation of Programmable IIR Filter for FPGA," 1st International Conference on Innovations in Signal Processing and Embedded systems (ICISPES-2021), Hyderabad, India, October 22-23, 2021.

- [33] K. C. Koteswaramma, Ande Shreya, N. Harsha Vardhan, Kantem Tarun, S. China Venkateswarlu, and Vallabhuni Vijay, "ASIC Implementation of division circuit using reversible logic gates applicable in ALUs," 1st International Conference on Innovations in Signal Processing and Embedded systems (ICISPES-2021), Hyderabad, India, October 22-23, 2021.

- [34] Vallabhuni Vijay, Pittala Chandra shekar, Shaik Sadulla, Putta Manoja, Rallabhandy Abhinaya, Merugu rachana, and Nakka nikhil, "Design and performance evaluation of energy efficient 8-bit ALU at ultra low supply voltages using FinFET with 20nm Technology," VLSI Architecture for Signal, Speech, and Image Processing, edited by Durgesh Nandan, Basant Kumar Mohanty, Sanjeev Kumar, Rajeev Kumar Arya, CRC press, 2021.

- [35] Vallabhuni Vijay, C. V. Sai Kumar Reddy, Chandra Shaker Pittala, Rajeev Ratna Vallabhuni, M. Saritha, M. Lavanya, S. China Venkateswarlu and M. Sreevani, "ECG Performance Validation Using Operational Transconductance Amplifier with Bias Current," International Journal of System Assurance Engineering and Management, vol. 12, iss. 6, 2021, pp. 1173-1179.

- [36] S. Swathi, S. Sushma, C. Devi Supraja, V. Bindusree, L. Babitha and Vallabhuni Vijay, "A Hierarchical Image Matting Model for Blood Vessel Segmentation in Retinal Images," International journal of system assurance engineering and management, vol. 13, iss. 3, 2022, pp. 1093-1101.

- [37] Bandi Mary Sowbhagya Rani, Vasumathi Devi Majety, Chandra Shaker Pittala, Vallabhuni Vijay, Kanumalli Satya Sandeep, Siripuri Kiran, "Road Identification Through Efficient Edge Segmentation Based on Morphological Operations," Traitement du Signal, vol. 38, no. 5, Oct. 2021, pp. 1503-1508.

- [38] M. Lavanya, Malla Jyothsna Priya, Ponukumatla Janet, Kavuluri Pavan Kalyan, and Vijay Vallabhuni, "Advanced 18nm FinFET Node Based Energy Efficient and High-Speed Data Comparator using SR Latch," International Conference On Advances In Signal Processing And Communication Engineering (ICASPACE 2021), Hyderabad, India, July 29-31, 2021.

- [39] J. Sravana, K.S. Indrani, Sankeerth Mahurkar, M. Pranathi, D. Rakesh Reddy, and Vijay Vallabhuni, "Optimised VLSI Design of Squaring Multiplier using Yavadunam Sutra through Deficiency Bits Reduction," International Conference On Advances In Signal Processing And Communication Engineering (ICASPACE 2021), Hyderabad, India, July 29-31, 2021.