Physical Design of Scalable Memristor Crossbars for Neuromorphic Computing

DOI:

https://doi.org/10.31838/JVCS/07.01.20Keywords:

Memristor, Crossbar Architecture, Neuromorphic Computing, System VerilogAbstract

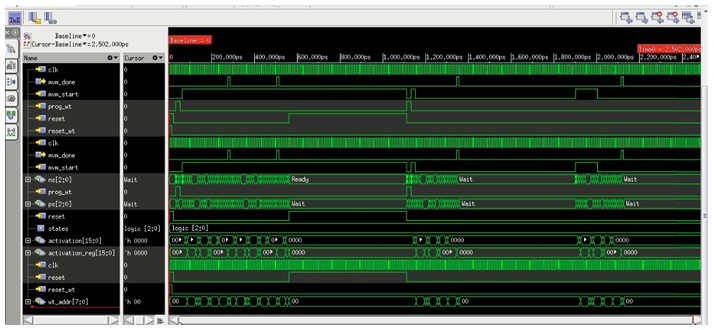

Neuromorphic computing represents a transformative direction in artificial intelligence (AI), offering energy-efficient, massively parallel processing inspired by the structure and function of biological neural systems. Memristor-based crossbar arrays serve as a foundational element in neuromorphic computing, offering the capability to perform in-memory operations essential for neural tasks such as matrix-vector multiplication. This work presents a structured approach to the design and synthesis of scalable crossbar architecture specifically intended for neuromorphic hardware. Emphasis is placed on achieving compact layout density while minimizing parasitic effects that typically hinder performance in dense integration. The architecture is rigorously evaluated through System Verilog simulations to verify functional accuracy and fault tolerance. Subsequent synthesis using Cadence Genus demonstrates measurable gains in power efficiency, area utilization, and timing performance. These outcomes underscore the architecture’s suitability for advanced neuromorphic processors, where reliability and computational efficiency are paramount. Through a cohesive integration of physical design strategies, simulation validation, and synthesis optimization, the proposed framework contributes meaningfully to the development of high-performance hardware for AI and machine learning applications.