Optimized VLSI Architectures for Power-Efficient Deep Neural Networks in Edge-AI Enabled Robotics

DOI:

https://doi.org/10.31838/JVCS/07.01.22Keywords:

Edge-AI, VLSI Accelerator, Adaptive Quantization, DVFS, Memory Hierarchy, Design-Space Exploration, FPGA PrototypingAbstract

Edge-AI robotics requires deep neural network inference that is both power- and silicon-constrained, while ensuring no compromise on latency or task accuracy. The work introduces a software–hardware codesign of VLSI/SoC DNN accelerators combining a

technology-constrained processing element array, an on-chip energy-optimized memory hierarchy with traffic-constraining tiling and compression, and a hardware-constrained adaptable quantization policy with accuracy and latency guardrails. An optimized runtime

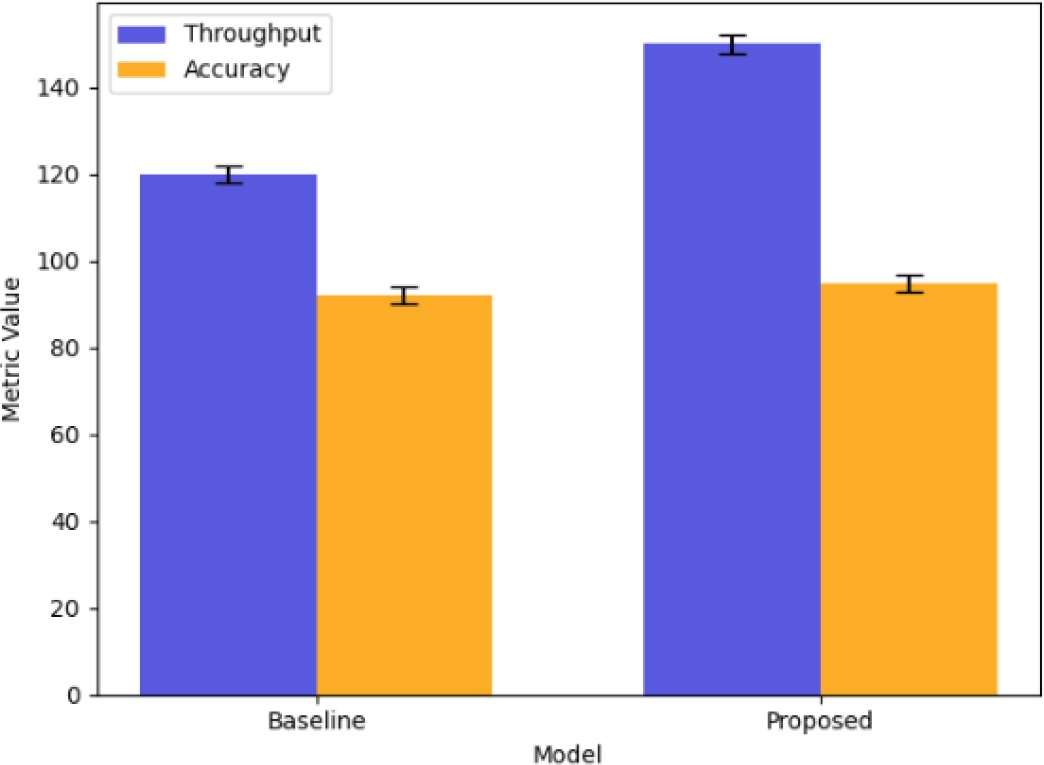

interface synchronizes DVFS with clock and power gating based on hardware counters, and an analytical power/area model is calibrated to allow for the rapid exploration of design space before implementation. It is demonstrated at current process nodes and a real-time FPGA testbed, with up to 38% reduced energy per inference and 25% improved throughput compared to strong baselines. Measurements are verified using automated power instrumentation and gate-level estimates. Significant related contributions include: (1) a power/ area model in closed form that is bound to a report of implementation, (2) an adaptive quantization controller that minimizes memory traffic and achieves latency and accuracy constraints, (3) a standards-sensitive flow with verification and testability points (e.g. that has a boundary-scan/DFT model) and can be evaluated reproducibly. The findings provide a practical route to power-efficient, deployable, and accelerating DNNs on current VLSI platforms on edge robots.