Energy-Aware VLSI Architectures for Intelligent Signal Processing in Neural Computing and Next-Generation IoT–Robotics Integration

DOI:

https://doi.org/10.31838/JVCS/07.01.27Keywords:

Energy-aware VLSI, in-memory computing, Adaptive DVFS, FD-SOI technology, Edge AI.Abstract

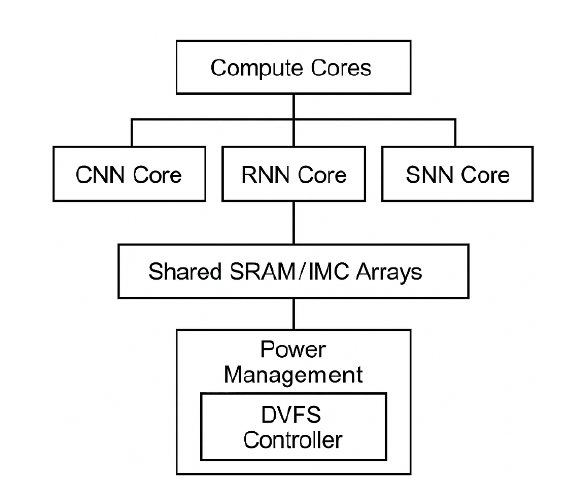

The recent accelerated growth of artificial intelligence (AI) in embedded and edge systems has further heightened the demand of energy-efficient VLSI architectures that can compute real time and multi-modal neural physics and computation with limited power and latency. The traditional von Neumann architectures fail to cope with these requirements because the cost of data exchange between processing and memory units is very high. To overcome this drawback, this contribution presents an energy-conscious neural VLSI system that incorporates convolutional (CNN), recurrent (RNN), and spiking (SNN) processing units in a single adaptive system. The design is fabricated with a 22 nm technology based on fully depleted silicon-on-insulator (FD-SOI) technology, dynamic voltage and frequency scaling (DVFS), hierarchical power gating, approximate arithmetic and in-memory computing (IMC) in order to maximize the trade-off between energy efficiency and computational throughput. A network-on-chip (NoC) reconfigurable interconnect allows workload to easily be migrated between neural domains and a firmware-level scheduler (S) as well as Linux-based middleware (M) offers realtime power management (S) and orchestration of workloads (M). The correct operation of hardware and software is confirmed by hardware/software co-simulation in ROS and Unity 3D. Experimental test on benchmark data, 300 VW on facial landmark tracking, Cornell Grasp on robotic perception and the UCI-HAR on sensor fusion indicate strong inference behaviour with an error margin of less than +1 percent deviation in accuracy with respect to floating-point counterparts. The fake prototype attains 5.2 TOPS/W and 0.35 pJ/MAC efficiency with the best comparisons with the similar edge accelerators in energy and area measures. These findings support the possibility of the suggested architecture to be used in wearable devices, autonomous drones, intelligent sensors, and other future IoT-robotics systems that will demand persistent, low-power intelligence.