An Efficient Error Resilient Ternary Content Addressable Memory Architecture

DOI:

https://doi.org/10.31838/JCVS/08.01.01Keywords:

Ternary Content Addressable Memory (TCAM), Soft error in data and parity bits, 2D parity, 3D parity, Hamming Codebased Error Correction, Error Correction Capability (ECC)Abstract

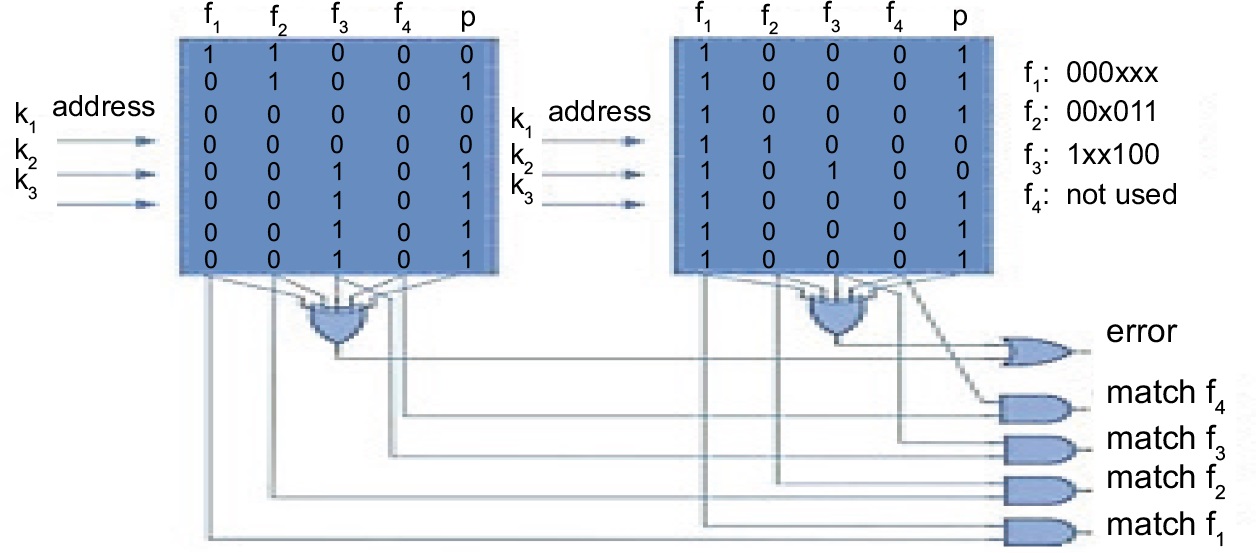

High-speed memories like TCAM (Ternary Content Addressable Memory) are widely employed in highthroughput search applications like network routers. Using ASIC (Application-Specific Integrated Circuits) to construct TCAM memories allows for a higher search rate at the expense of increased power and resource requirements. However, safeguarding the TCAM from soft errors while maintaining good search speed and minimizing critical path time is a difficult task. In this paper, we present a TCAM architecture with a multipumping technique that incorporates the correction of multiple bits using the Hamming code. Different sizes, such as 4x4, 16x8 and 32x16, of the proposed TCAM architecture are simulated and implemented in 45nm technology. The proposed work evaluates

the TCAM in comparison to the Look-Up Table (LUT) based on a priority encoder in TCAM architecture, Two-Dimensional (2D) parity, Three-Dimensional (3D) parity, and Hamming code-based error correction methods with a multiplexer block in TCAM architecture. The results demonstrate that the suggested TCAM has a lesser delay compared to the LUT-based and higher error

correction capability, including the parity bits.