Implementation of an Efficient RISC-V Processor Featuring a Novel Gshare Branch Prediction Technique

DOI:

https://doi.org/10.31838/JCVS/07.02.08Keywords:

RISC-V, VLSI, Branch prediction, Gshare, BTB, PHT, GHRAbstract

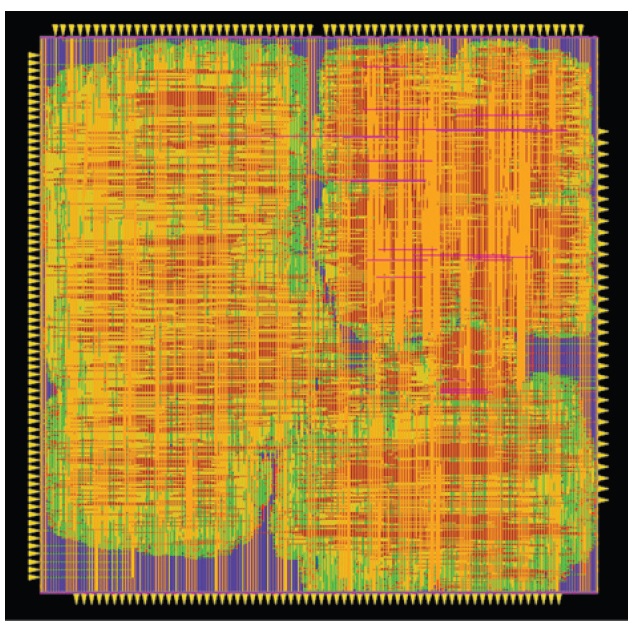

RISC-V, characterized by its straightforward and open-source instruction set design, is becoming a compelling platform for contemporary IoT devices. Dynamic branch prediction, especially two-level methods and history/address hashing approaches such as Gshare, has demonstrated significant efficacy in alleviating control hazards in pipelined processors. This study introduces a 5-stage (IF–ID–EX–MEM–WB) RISC-V core that incorporates a Branch Prediction Unit (BPU), which merges a Branch Target Buffer (BTB) and a Pattern History Table (PHT) featuring 256 entries with 2-bit saturating counters. The PHT index is derived from XOR(GHR, PC[9:2]), while the BTB is refreshed utilizing the lower 8 bits of the PC. The design was executed from RTL to GDSII with Cadence Genus, Conformal, and Innovus on GPDK045 (45 nm) technology, illustrating feasibility beyond research confined to RTL or FPGA, such as RVCoreP. RTL simulation verified the accurate execution of all 37 RV32I instructions and attained roughly 90.4% accuracy in branch prediction for branch-intensive tasks. Post-layout results indicate that the design attained the target frequency (exceeding 50 megahertz), with a recorded maximum frequency of roughly 75 MHz. The overall power consumption of the core is around 15.078 mW across an area of roughly 0.69 mm², resulting in a core density of nearly 70 percent. These data validate the feasibility of employing two-level branch prediction in lightweight RISC-V microcontrollers.