Energy-Efficient VLSI Architecture for Time-Multiplexed Vibration Feature Extraction and Fuzzy Inference

DOI:

https://doi.org/10.31838/JVCS/07.02.11Keywords:

Low-power VLSI, Integer FIS, vibration feature extraction, Time-multiplexed architecture, low-power edge processingAbstract

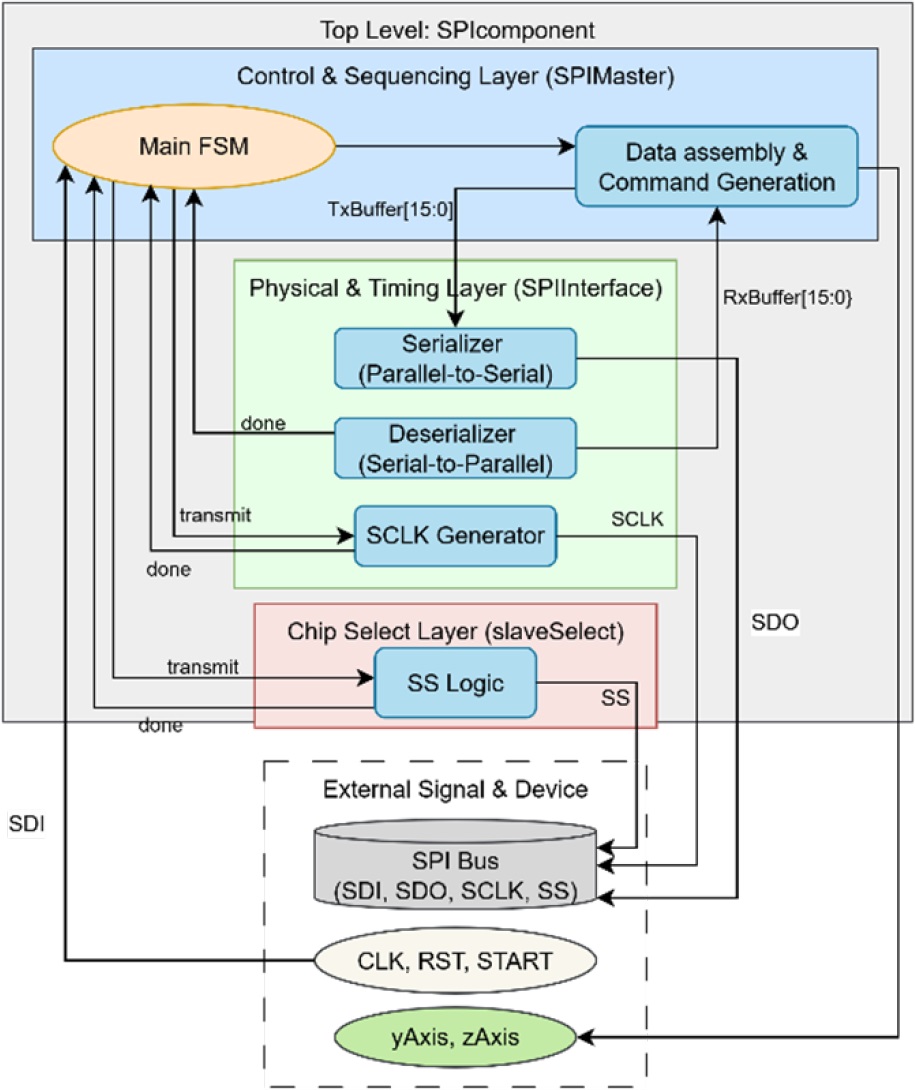

This paper presents an energy-efficient VLSI architecture for time-multiplexed vibration feature extraction and fuzzy inference targeted at conveyor gearbox condition monitoring. A triaxial ADXL345 accelerometer mounted on the gearbox housing is sampled at 50 Hz, and ten integer time-domain features are computed over 1 s windows. Pearson correlation analysis identifies three dominant features—z-axis peak-to-peak, z-axis Willison amplitude, and y-axis Willison amplitude—which form the inputs of a three-class fuzzy inference system (Normal, Scoring, Damaged). The proposed architecture integrates a digital sensor interface, a two-stage feature-extraction block, and a three-stage fuzzification–inference–defuzzification pipeline using fixed-point arithmetic and extensive time-multiplexing. Two implementations, with 8-bit and 4-bit word-lengths, are prototyped on a small low-power programmable logic device. The 4-bit variant reduces logic-cell usage from 5105 (66%) to 3550 (46%) and lowers estimated total power from 15.42 mW to 12.46 mW, while maintaining high recall for damaged gears (97% to 96%) and sub-millisecond end-to-end latency per decision. Power figures are obtained from vendor models using post-route netlists and simulated switching activity and are reported together with an effective energy-per-decision estimate to characterize the suitability of the proposed architecture for battery-powered edge deployments.