SWS-FET-Based Quaternary Magnitude Comparator: Design and Simulation

DOI:

https://doi.org/10.31838/JVCS/07.02.13Keywords:

Quaternary Magnitude Comparator, SWS-FET, Multivalued Logic, Nanostructure Devices, High Speed Arithmetic CircuitsAbstract

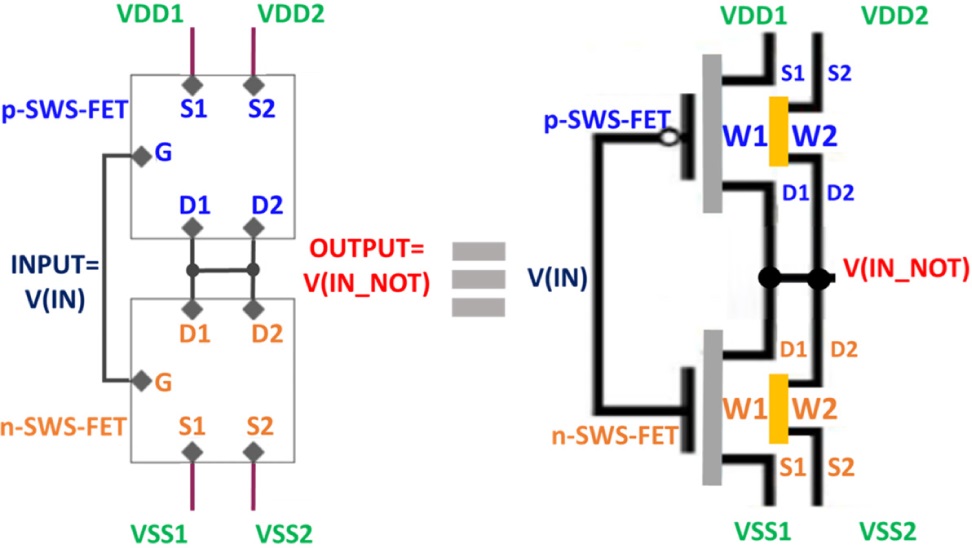

This article presents a quaternary magnitude comparator (QMC) implemented using spatial wavefunction-switched FETs (SWS-FETs). The native multistate conduction of SWS-FETs eliminates binary–quaternary conversion overhead and reduces transistor count, delay, and power. A one-digit QMC (two-bit) is validated in Cadence at the 180 nm node, achieving 0.14 ns delay and 96 μW total power. A 64-bit instance achieves 0.46 ns delay at 4.84 FO4, where FO4 denotes the fan-out-of-4 inverter delay used as a normalized timing metric,

with only 0.79 μW/MHz power. The architecture scales efficiently up to 1024 bits, exhibiting near-linear delay growth from 0.14 ns to 0.72 ns and controlled power up to 12.67 μW/MHz. Compared to CMOS implementations, the proposed SWS-FET QMC demonstrates

lower delay, reduced area, and improved energy efficiency, confirming its suitability for compact multivalued arithmetic systems.