Energy-Efficient Neural Network Accelerator Design for Real-Time DSP and Cryptographic Processing Using Advanced VLSI Architectures

DOI:

https://doi.org/10.31838/JCVS/07.02.06Keywords:

Neural Network Accelerators, Energy-Efficient VLSI, Real-Time DSP, Cryptographic Hardware, Systolic Arrays, Hardware-Aware OptimizationAbstract

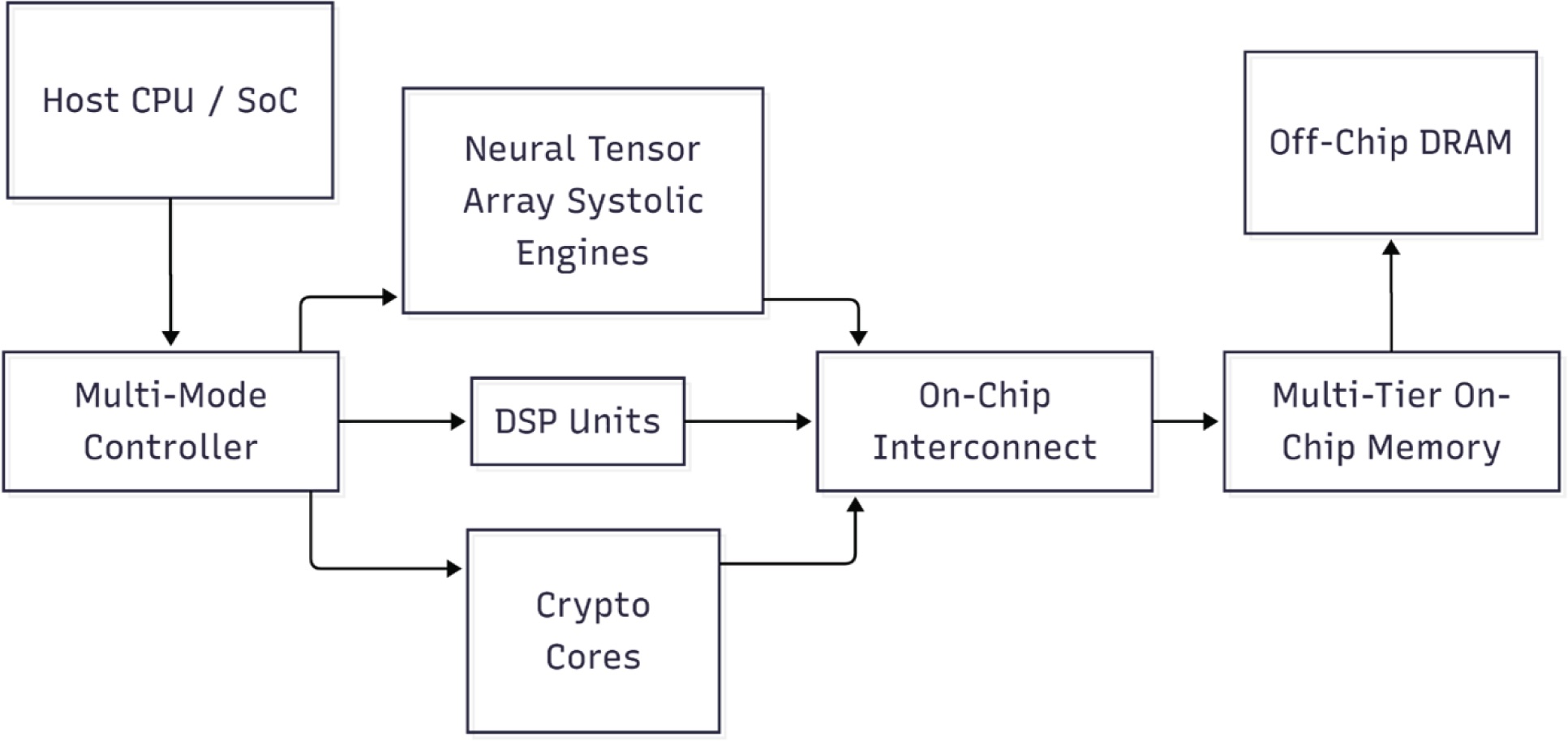

The development of artificial intelligence, real-time digital signal processing (DSP) and cryptographic workloads have been fueling the need to have highly efficient neural network accelerators embedded within state-of-the-art VLSI architectures. Traditional accelerators that are optimised to either DSP or cryptography are no longer capable of supporting the power, latency, and throughput requirements of the current embedded and high-performance computing systems. With the increasing complexity of neural workloads and the increasing security assurances needed with cryptographic operations, energy efficiency is becoming more important than ever. It is a unified, energy efficient accelerator design which combines the use of neural processing, DSP kernels, and cryptographic primitives, in a single VLSI system. The framework suggested utilizes hardware-aware quantization, systolic TA, reconfigurable DSP pipeline, and low-power cryptographic cores designed with the aid of machine learning-driven design frameworks. Learning is performed to search through architectural designs via reinforcement learning, and the single-objective bi-objective-optimization is directed by hardware-aware optimization of performance in terms of area, power and latency. Improved throughput-per-watt, low-latency processing and secure execution is experimentally proven using 7 nm and 5 nm design nodes compared to current accelerator designs. The findings indicate that the suggested architecture can be effectively applied to AI-based embedded systems, secure IoT systems, and real time edge intelligence that requires co-location of DSP and cryptographic operation. This paper adds a scalable energy aware VLSI accelerator design that can address the increased computational and security requirements of the next generation intelligent systems.