AI-Optimized Low-Power VLSI Solutions for Implantable Biomedical Devices Integrating Neural Networks and Bio-Signal DSP

DOI:

https://doi.org/10.31838/JCVS/07.02.03Keywords:

Low-Power VLSI, Biomedical Implants, Neural Network Accelerators, Bio-Signal DSP, AI Hardware, Energy OptimizationAbstract

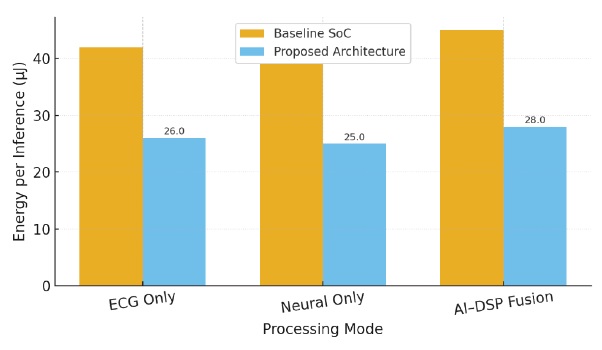

Biomedical devices that are implantable are increasingly based on on-chip intelligence and low-power computing as well as secure processing of physiological signals to facilitate continuous monitoring and closed-loop intervention. Conventional VLSI design systems are unable to satisfy the high power, latency, and reliability requirements of any long-term implantable system, particularly with neural-network inference and bio-signal DSP pipelines becoming the new norm with next-generation medical implants. The following paper describes an AI-based low-power VLSI design system with neural inference engines, real time physiological DSP, and adaptive power optimization designed specifically to be used in implantable systems. To reduce dynamic switching energy, optimise arithmetic precision and speed up convolutional bio-signal processing, machine learning is incorporated throughout the design process. An optimization framework with multiple objectives is used in order to meet the biomedical requirements of thermal safety, battery life, and energy restrictions that are biocompatible. The physics of simulation with 65 nm and 28 nm low-leakage CMOS nodes show that they can significantly reduce energy usage, increase the level of classification of neural and ECG signals, and become more resistant to signal artefacts. The suggested architecture proves to be highly suitable in pacemakers, neural prosthetics, wearable-implant hybrids and intelligent drug-delivery implantable devices that need continuous low-power AI-supported functionality. The work sets a common ground towards the combination of neural inference, DSP, and biomedical safety aspects to the next-generation implantable VLSI platforms.