Design and Analysis of 4-bit Reconfigurable Johnson Counter using 18nm finFET

DOI:

https://doi.org/10.31838/jvcs/08.01.04Keywords:

Johnson Counter, Flip-flop, finFETAbstract

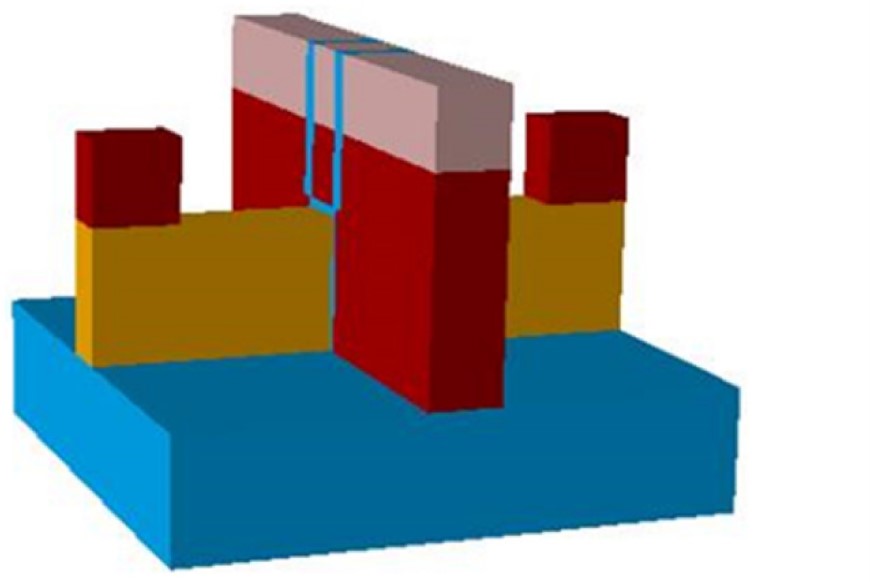

The counter is used widely as an important component in measurement systems. Hybrid logic has one prominent advantage in the construction of counter circuits because it requires a minimal number of transistors and demands low power. This work is a reconfigurable 4-bits Johnson counter. When the mode is set to one, the counter is used for counting. In this configuration, the flip - flops are initialized after four clock cycles provided that the reset (RST) signal is low. If RST is high then the counter performs its normal counting operation. When mode is off the counter is changed by resetting the last bit of the count vector to its initial value. The flip flip is the basic component of the proposed counter. To realize a low power, high speed and low complexity counter, we implemented a mixed logic flip flop. This flip flop is realized using 18 transistors, that is 9 PFETs and 9 NFETs. It is just made up of complementary logic and pass gate transistor and has succeeded in terms of increase speed, power and circuit complexity. The obtained results were achieved using Cadence Virtuoso at finFET technology node 18nm. Experiments were done in different process corners, with supply voltages ranging from 0.7V to 1.0V, and temperatures varying from -25 0C to 75 0C. Based on the results, the proposed counter shows tremendous stability.