Design and Verification of FPGA-based Range Processing, Peak Detection and Doppler Processing for FMCW-RADAR

DOI:

https://doi.org/10.31838/jvcs/08.01.05Keywords:

FPGA, FFT, AXI, FMCW Radar, Doppler, Target detectionAbstract

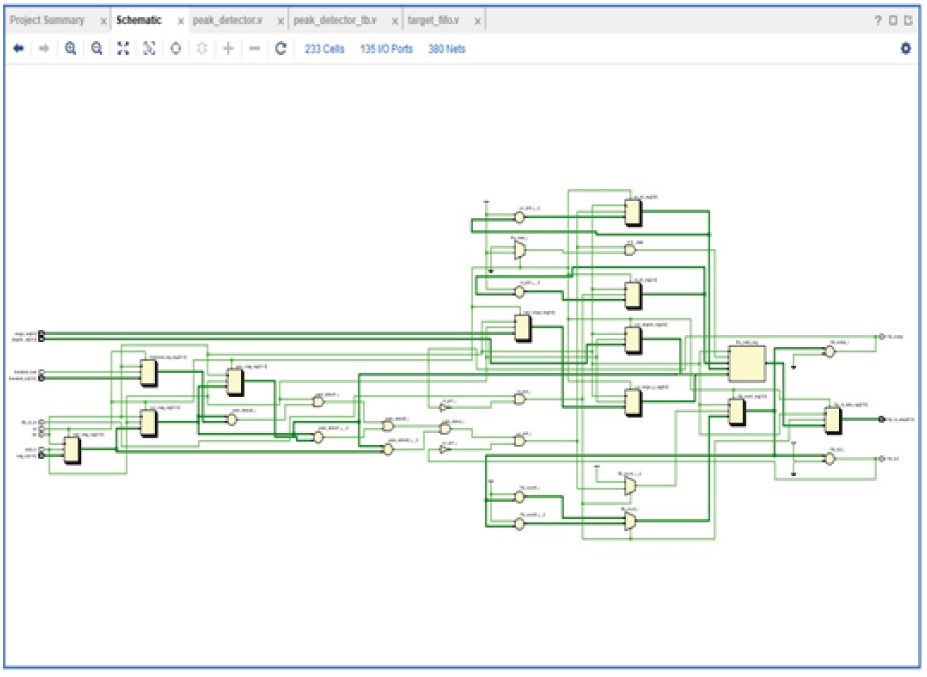

Modern RADAR systems produce a large amount of data that must be processed quickly and accurately for reliable target detection. Software-based processing methods often struggle to meet real-time requirements due to high latency and computational overhead. This work presents a fully streaming, Field Programmable Gate Array (FPGA)-based peak detection architecture tightly integrated within the Range–Doppler processing pipeline. Continuous magnitude data from the Range and Doppler Fast Fourier Transform (FFT) stages is transferred using an Advanced eXtensible Interface (AXI)-Stream interface, enabling seamless integration between Xilinx FFT IP cores and a custom peak detection accelerator without intermediate memory storage. Unlike conventional radar systems that construct a two-dimensional Range–Doppler map followed by explicit scanning, the proposed approach performs detection on a linearized data stream. This eliminates the need for complex 2D search logic, reduces control overhead, and enables low-latency,

real-time operation suitable for practical radar deployments. Additionally, index-aware detection logic propagates range and Doppler indices alongside magnitude data, enabling direct extraction of target coordinates without post-processing. The modular AXI-Stream architecture ensures reusability, timing-closed operation, and reduced FPGA resource utilization compared to reference designs. The proposed system emphasizes FPGA-focused architectural optimization rather than algorithm-level modification, distinguishing it from

prior software-oriented or hybrid detection approaches. The complete processing chain achieves an end-to-end latency of approximately 1.1 ms for a full frame comprising 64 chirps, while sustaining a continuous input data rate exceeding 200 MSamples/s. The design was synthesized and simulated using the Xilinx Vivado design tool and implemented on a Zynq-7000-based ZC702 evaluation board, demonstrating efficient FPGA resource utilization of approximately 35% LUTs, 28% flip-flops, 42% BRAM, and 6 DSP slices. Simulation results confirm correct FFT operation, reliable buffering, and accurate peak detection across varying signal-to-noise ratios. The proposed architecture offers low latency, high throughput, and efficient hardware utilization, making it well-suited for practical real-time radar signal processing applications. Overall, the proposed FPGA-based solution demonstrates low latency, efficient resource usage, and reliable real-time performance, making it suitable for practical Frequency Modulated Continuous Wave (FMCW)-RADAR signal processing applications.