Efficient Design of Up Sampler and Down Sampler using Single Electron Transistor-Metal Oxide Semiconductor Field Effect Transistor

DOI:

https://doi.org/10.31838/jvcs/07.01.05Keywords:

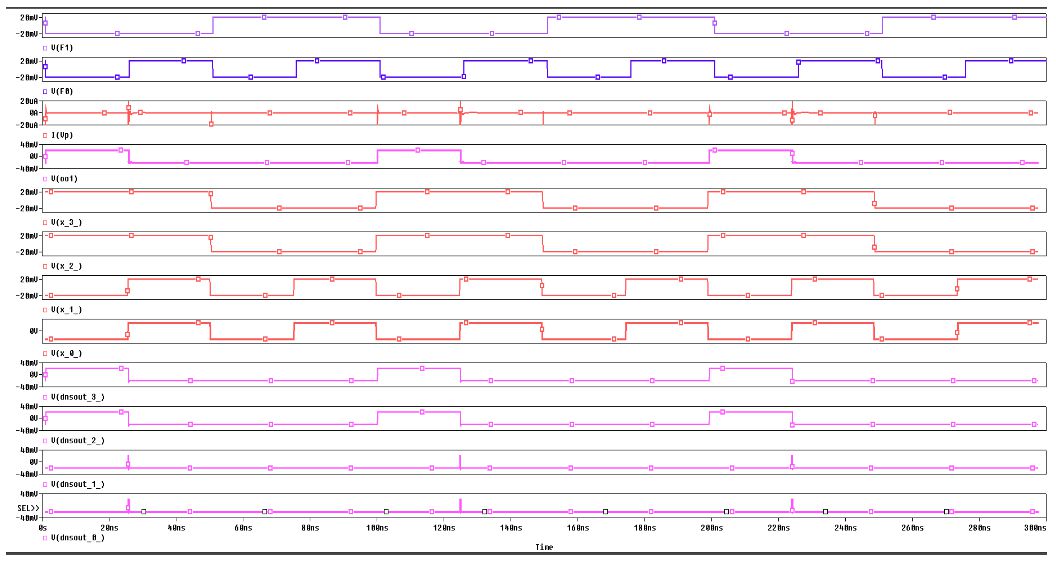

Down Sampler, Up Sampler, Single Electron Transistor, Complementary MOSFETAbstract

The increasing demand for high performance and low power, energy efficient electronics has led to significant advancements in nanoscale devices. Among these the single electron transistor (SET) stands out due to its potential for ultra low power consumption and high sensitivity. This article presents an in depth study on the efficient design of SET based up samplers and down samplers. These components are crucial in modern communication systems for converting signals between different sampling rates. Our findings indicate that SETs offer substantial potential for reducing power consumption and enhancing the precision of sampling rate conversions although challenges such as thermal stability and integration with existing systems remain. This study aims to contribute to the development of more efficient and compact communication technologies by leveraging the unique properties of SETs.