Efficient VLSI Architecture Integrating Vedic Mathematics for Square Computation

DOI:

https://doi.org/10.31838/jvcs/07.01.09Keywords:

Vedic mathematics, , Urdhva-Tiryagbhyam Sutra, , FPGA,, Spartan-7, , Artix-7, , Virtex-4,, Multiplier circuit, , Booth multiplier.Abstract

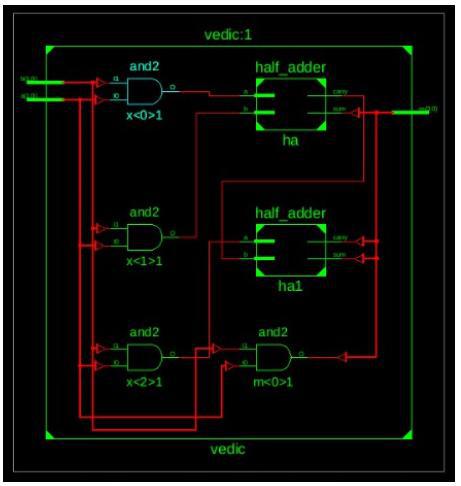

Implementation of combinational logic circuits in combination with Vedic maths sutra has many advantages over traditional multiplier circuits, such as reduced time delay, less resource utilization, and less power consumption by the selection of the proper FPGA family. Multiplication is one of the important instructions used for performing complex operations in DSP processors. The proposed paper presents the use of Urdhva-Tiryagbhyam Sutra for the square operation. The results of the designed Vedic circuit show that, there is a 17.36% reduction in time delay and an 8.13% reduction in power consumption in Spartan-7 than Artix-7. There is a 33.6% reduced time delay than the Nikhilam sutra, 45.87% reduced delay than the Yavadunam sutra, 87.07% less delay than the Booth multiplier, and 67.83% reduced delay than Booth Wallace multiplier. Thus, implementing the Vedic Sutra for finding the square of a given number causes a reduction in time delay, power consumption and small chip size.