Energy-Efficient GNRFET-Based Ternary Full Adder for Next-Generation Integrated Circuits

DOI:

https://doi.org/10.31838/jvcs/07.01.12Abstract

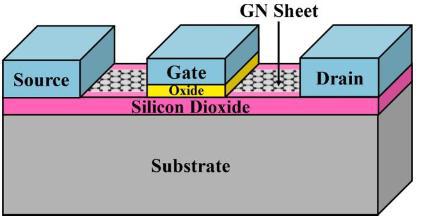

Ternary logic is an appealing alternative to binary logic, because it reduces circuit complexity, implementation area, and power consumption. This paper covers Graphene Nanoribbon Field Effect Transistor (GNRFET) based Ternary Full Adder (TFA) used for Next Generation Integrated Circuits. Instead of utilizing two states, ternary logic uses three states to execute efficiently in computation and data processing. This significantly reduces the complexity of the arithmetic circuit, making it suitable for high-speed applications. New technology, based on GNRFET, proposed as possible successor to CMOS technology. Proposed TFA1 and TFA2 with 98 transistors and 68 transistors, simulated using the HSPICE Simulator with 32nm MOS-GNRFET Nano Hub Models. Simulated results reveal that the proposed TFA2 has reduced Power Delay Product (PDP) than the proposed TFA1 approach. The most essential parameter of digital circuit design used in Multi Valued Logic (MVL) is the threshold voltage of GNRFET, changed in ternary logic to reduce power consumption and delay. Low power consumption and fast processing of these circuits make it suitable for the next-generation integrated circuits