VLSI-Optimized Post-Quantum Cryptographic Architecture for Secure IoT and Blockchain Applications

DOI:

https://doi.org/10.31838/jvcs/07.01.14Keywords:

Secure IoT , Frameworks, , Lattice-Based Encryption, , VLSI Optimisation, , Quantum-Resistant Cryptography, , ASIC-FPGA IntegrationAbstract

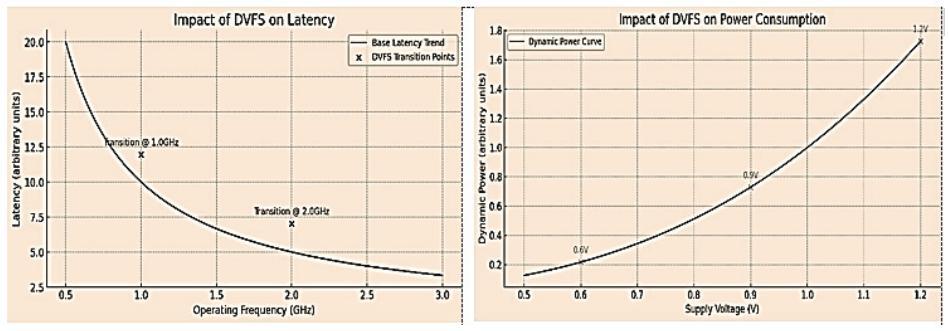

With the rapidly evolving background of cryptography, it is crucial to remain one step ahead of potential threats and employ the newest technologies. This research presents an enhanced LUT–CLA–QTL implementation with the addition of quantum-resistant algorithms for the prevention of quantum computer advancement. The approach employs lattice-based encryption to provide robust security with the addition of state-of-the art semiconductor nodes like 7nm technology for area, power, and delay reduction. The solution employs hybrid FPGA-ASIC designs with flexibility-performing balance. Additionally, side-channel attack resistance and fault tolerance are integrated for end-to-end security. Dynamic voltage and frequency scaling (DVFS) enhances power efficiency, and parallel processing enhances throughput and lowers latency. The novel solution addresses the need for effective, secure cryptographic devices in limited environments, including IoT devices, blockchain, and secure data communication protocols. In comparison to conventional methods, experimental outcomes reflect outstanding improvements in ASIC performance metrics such as area, power dissipation, delay, APP, and ADP. The quantum resistant LUT–CLA–QTL structure possesses high quantum attack resilience, which makes it a forward-looking contender for today’s cryptographic applications. Future work includes optimization and verification of the structure using additional real-world usage to maintain its applicability and performance in different technological environments.