Energy-Efficient High Performance 64-bit ALU using Reversible Logic Based on Self Error Detection and Correction Technique

DOI:

https://doi.org/10.31838/JVCS/07.01.21Keywords:

FPGA, ALU, Reversible Logic, Majority Gate, Array Multiplier, Processor Design, Parity Checking, ECCAbstract

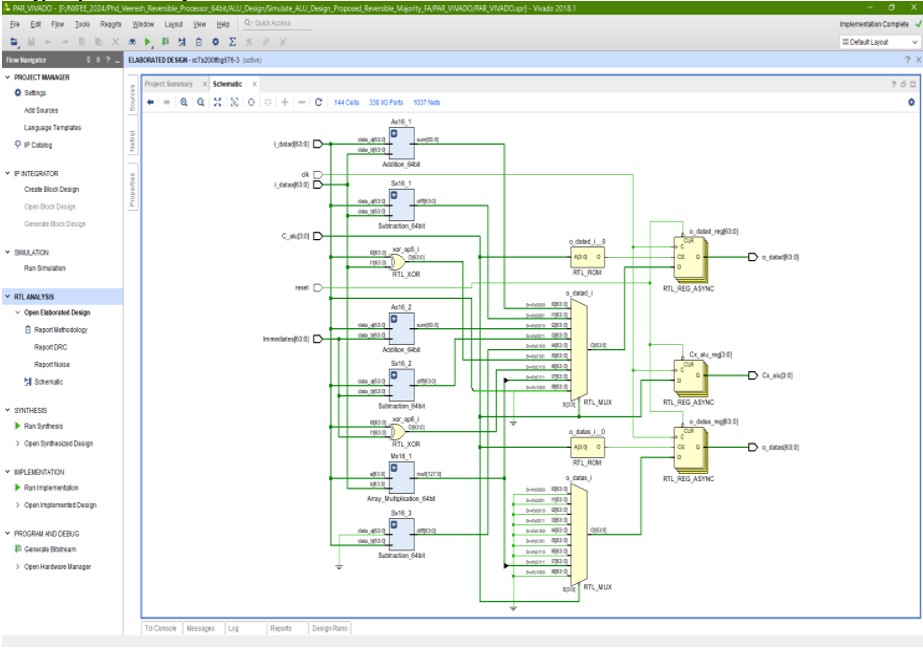

The aim of this research proposal is to design a self-error detection–based arithmetic operations unit, which is widely required in today’s AI technology for performing high-speed calculations of arithmetic and logical operations, and is a top priority in deep learning algorithms. In the proposed method, a high-speed and double precision arithmetic and logic unit (ALU) is designed, which employs reversible majority gate technology along with parity checking and error-correcting codes (ECC) to improve fault tolerance for low power computing systems. Reversible logic gates are given high priority in larger circuit designs and the use of more FPGA resources, as they reduce garbage signals and critical path delay in combinational design architecture. This reversible logic reduces the signal path and increases energy efficiency. Furthermore, to simplify complex logic operations, the novelty architecture designed a full adder using the majority logic (ML) gate, which uses reversible methodology that is specially used for Feynman and Toffoli gates. For self error correction, parity checking is utilized to identify single-bit mistakes, whereas Hamming code–based error correction was also included for multibit mistakes, and these hybrid implementations are helpful to detect and rectify errors. Furthermore, the proposed ALU facilitates fundamental operations such as addition, subtraction, and multiplication, which are designed with the proposed ML full adder architecture and finally evaluated for decreased power consumption and enhanced error resistance. The proposed design, synthesized and tested on the Xilinx Vivado Artix-7 FPGA platform, exhibits up to 52% reduced power consumption and utilizes 7.5% fewer LUTs than traditional designs.